- 您现在的位置:买卖IC网 > PDF目录376258 > PSD301-20JI (意法半导体) Low Cost Field Programmable Microcontroller Peripherals PDF资料下载

参数资料

| 型号: | PSD301-20JI |

| 厂商: | 意法半导体 |

| 英文描述: | Low Cost Field Programmable Microcontroller Peripherals |

| 中文描述: | 低成本现场可编程微控制器外围设备 |

| 文件页数: | 19/85页 |

| 文件大小: | 691K |

| 代理商: | PSD301-20JI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页

PSD3XX Famly

16

10.0

I/OPort

Functions

(

cont.)

10.2 Port A (PA0-PA7)

The control registers of Port A are located in CSIOPORT space; see Table 5.

10.2.1 Port A (PA0-PA7) in Multiplexed Address/Data Mode

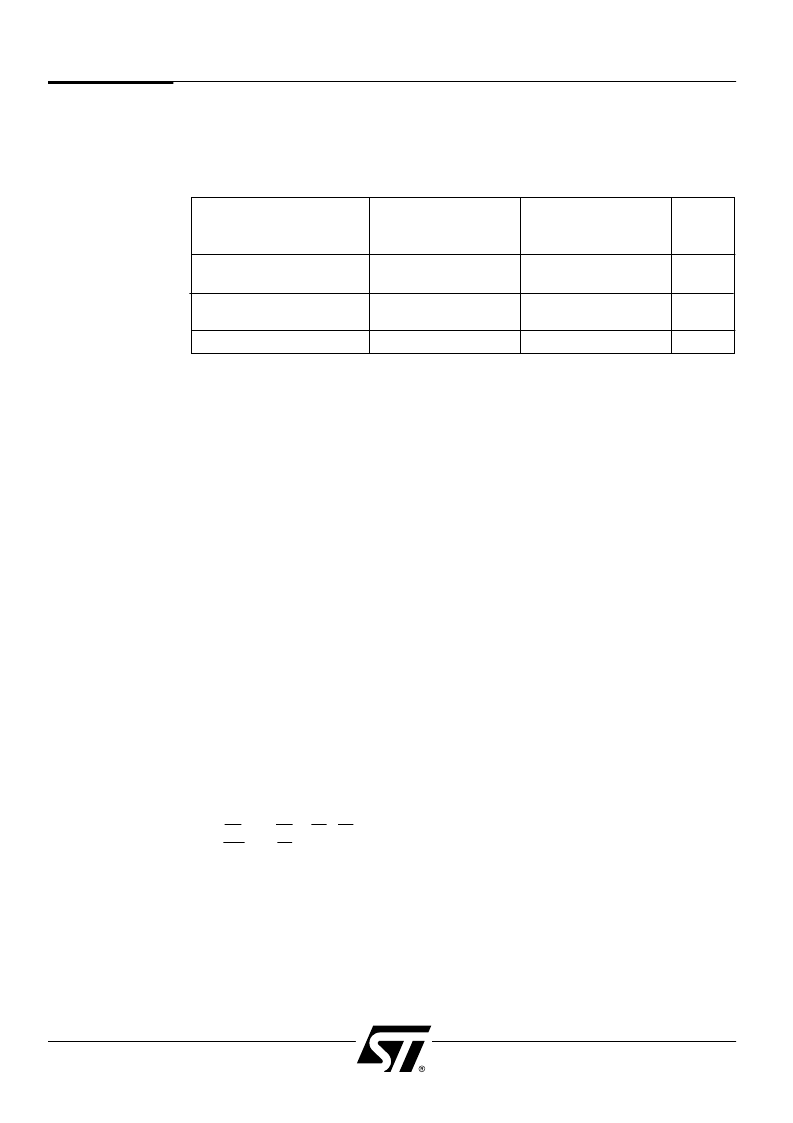

Each pin of Port A can be individually configured. The following table summarizes what the

control registers (in CSIOPORT space) for Port A do:

NOTE:

1. Default value is the value after reset.

Default

Value

(Note 1)

Register Name

0 Value

1 Value

Port A Pin Register

Sampled logic level

at pin = ‘0’

Pin is configured

as input

Data in DFF = ‘0’

Sampled logic level

at pin = ‘1’

Pin is configured

as output

Data in DFF = ‘1’

X

Port A Direction Register

0

Port A Data Register

0

MCUI/OMode

The default configuration of Port A is MCU I/O. In this mode, every pin can be set (at run-

time) as an input or output by writing to the respective pin’s direction flip-flop (DIR FF,

Figure 5A). As an output, the pin level can be controlled by writing to the respective pin’s

data flip-flop (DFF, Figure 5A). The Pin Register can be read to determine logic level of the

pin. The contents of the Pin Register indicate the true state of the PSD driving the pin

through the DFF or an external source driving the pin. Pins can be configured as CMOS

or open-drain using

ST

’s PSDsoft software. Open-drain pins require external pull-up

resistors.

Latched Address Output Mode

Alternatively, any bit(s) of Port A can be configured to output low-order demultiplexed

address bus bit. The address is provided by the internal PSD address latch, which latches

the address on the trailing edge of ALE/AS. Port A then outputs the desired demultiplexed

address bits. This feature can eliminate the need for an external latch (for example:

74LS373) if you have devices that require low-order latched address bits. Although any pin

of Port A may output an address signal, the pin is position-dependent. In other words, pin

PA0 of Port A may only pass A0, PA1 only A1, and so on.

Track Mode

Track Mode sets the entire port to track the signals on AD0/A0-AD7/A7, depending on

specific address ranges defined by the PAD’s CSADIN, CSADOUT1, and CSADOUT2

signals. This feature lets the user interface the microcontroller to shared external resources

without requiring external buffers and decoders. In Track Mode, Port A effectively operates

as a bi-directional buffer, allowing external MCUs or host processors to access the local

data bus. Keep the following information in mind when setting up Track Mode:

J

The direction is controlled by:

ALE/AS

RD/E or RD/E/DS (DS on non-3X1 devices only)

WR or R/W

PAD outputs CSADOUT1, CSADOUT2, and CSADIN defined in PSDsoft design.

J

When CSADOUT1 and ALE/AS are true, the address on AD0/A0-AD7/A7 is output on

Port A. Note: carefully check the generation of CSADOUT1 to ensure that it is stable

during the ALE/AS pulse.

J

When CSADOUT2 is active and a write operation is performed, the data on the

AD0/A0-AD7/A7 input pins flows out through Port A.

J

When CSADIN is active and a read operation is performed, the data on Port A flows

out through the AD0/A0-AD7/A7 pins.

J

Port A is tri-stated when none of the above conditions exist.

相关PDF资料 |

PDF描述 |

|---|---|

| PSD301-20JM | Low Cost Field Programmable Microcontroller Peripherals |

| PSD953212MIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD814F2-12 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD814F2-15 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD814F2-20 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD301-20JM | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| PSD301-20LI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Peripheral |

| PSD301-20LM | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Peripheral |

| PSD301-20Q | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Peripheral |

| PSD301-20QI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Peripheral |

发布紧急采购,3分钟左右您将得到回复。