- 您现在的位置:买卖IC网 > PDF目录368223 > PSD4135G1-A-15B81 (意法半导体) Flash In-System-Programmable Peripherals for 16-Bit MCUs PDF资料下载

参数资料

| 型号: | PSD4135G1-A-15B81 |

| 厂商: | 意法半导体 |

| 英文描述: | Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| 中文描述: | Flash在系统可编程外设的16位微控制器 |

| 文件页数: | 16/93页 |

| 文件大小: | 503K |

| 代理商: | PSD4135G1-A-15B81 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

Preliminary Information

PSD4000 Series

13

8.0

Register Bit

Definition

(cont.)

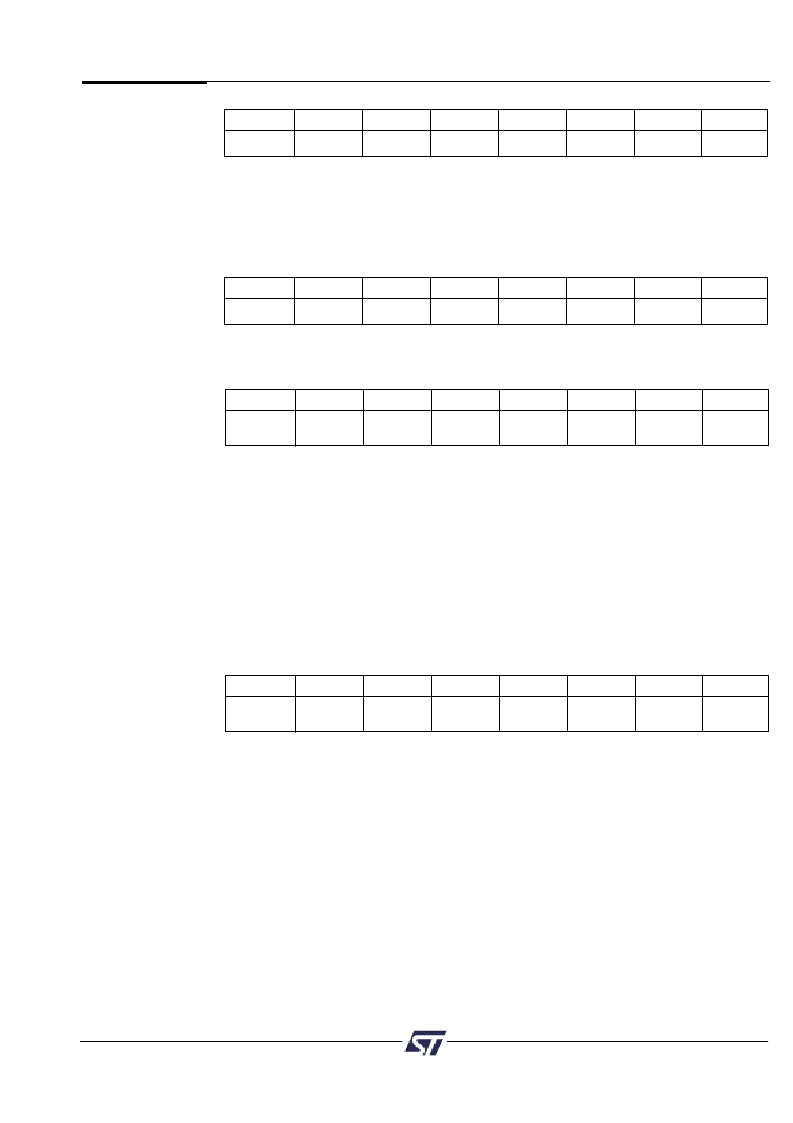

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Security_Bit

*

*

*

Sec3_Prot

Sec2_Prot

Sec1_Prot Sec0_Prot

Flash Boot Protection Register

Bit definitions:

Sec<i>_Prot

Sec<i>_Prot

1 = Boot Block Sector <i> is write protected.

0 = Boot Block Sector <i> is not write protected.

Security_Bit

0 = Security Bit in device has not been set.

1 = Security Bit in device has been set.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pgr7

Pgr6

Pgr5

Pgr4

Pgr3

Pgr2

Pgr1

Pgr0

Page Register

Bit definitions:

Configure Page input to PLD. Default Pgr[7:0] = 00.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

*

*

PLD

PLD

array-clk

PLD

Turbo

*

APD

enable

*

Mcells clk

PMMR0 Register

Bit definitions: (default is 0)

Bit 1 0 = Automatic Power Down (APD) is disabled.

1 = Automatic Power Down (APD) is enabled.

Bit 3 0 = PLD Turbo is on.

1 = PLD Turbo is off, saving power.

Bit 4 0 = CLKIN input to the PLD AND array is connected.

Every CLKIN change will power up the PLD when Turbo bit is off.

1 = CLKIN input to PLD AND array is disconnected, saving power.

Bit 5 0 = CLKIN input to the PLD Micro

Cells is connected.

1 = CLKIN input to the PLD Micro

Cells is disconnected, saving power.

*

Not used bit should be set to zero.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

*

PLD

PLD

PLD

PLD

PLD

*

*

array WRh

array Ale

array Cntl2 array Cntl1 array Cntl0

PMMR2 Register

Bit definitions (defauld is 0):

Bit 0 0 = Address A[7:0] are connected into the PLD array.

1 = Address A[7:0] are blocked from the PLD array, saving power.

Note: in XA mode, A3-0 come from PF3-0 and A7-4 come from ADIO7-4.

Bit 2 0 = Cntl0 input to the PLD AND array is connected.

1 = Cntl0 input to the PLD AND array is disconnected, saving power.

Bit 3 0 = Cntl1 input to the PLD AND array is connected.

1 = Cntl1 input to the PLD AND array is disconnected, saving power.

Bit 4 0 = Cntl2 input to the PLD AND array is connected.

1 = Cntl2 input to the PLD AND array is disconnected, saving power.

Bit 5 0 = Ale input to the PLD AND array is connected.

1 = Ale input to the PLD AND array is disconnected, saving power.

Bit 6 0 = WRh/DBE input to the PLD AND array is connected.

1 = WRh/DBE input to the PLD AND array is disconnected, saving power.

*

Not used bit should be set to zero.

相关PDF资料 |

PDF描述 |

|---|---|

| PSD4135F2-A-15B81 | Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4135G2-A-15B81 | Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4135F3-A-15B81 | Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4135G3-A-15B81 | Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4135F1V-A-15B81 | Flash In-System-Programmable Peripherals for 16-Bit MCUs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD4135G1-A-15B81I | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4135G1-A-15J | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4135G1-A-15JI | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4135G1-A-15M | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4135G1-A-15MI | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System-Programmable Peripherals for 16-Bit MCUs |

发布紧急采购,3分钟左右您将得到回复。