- 您现在的位置:买卖IC网 > PDF目录376279 > PSD8543V15JIT (意法半导体) 3.3V, 8-Bit to 4-Bit, Mux/DeMux Fast Ethernet LAN Switch (Single Enable) w/LED Switching PDF资料下载

参数资料

| 型号: | PSD8543V15JIT |

| 厂商: | 意法半导体 |

| 英文描述: | 3.3V, 8-Bit to 4-Bit, Mux/DeMux Fast Ethernet LAN Switch (Single Enable) w/LED Switching |

| 中文描述: | Flash在系统可编程ISP的外设的8位微控制器 |

| 文件页数: | 55/110页 |

| 文件大小: | 1737K |

| 代理商: | PSD8543V15JIT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页当前第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

55/110

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

Address In Mode

For MCUs that have more than 16 address sig-

nals, the higher addresses can be connected to

Port A, B, C, and D. The address input can be

latched in the Input Macrocell (IMC) by Address

Strobe (ALE/AS, PD0). Any input that is included

in the DPLD equations for the SRAM, or primary or

secondary Flash memory is considered to be an

address input.

Data Port Mode

Port A can be used as a data bus port for a MCU

with a non-multiplexed address/data bus. The

Data Port is connected to the data bus of the MCU.

The general I/O functions are disabled in Port A if

the port is configured as a Data Port.

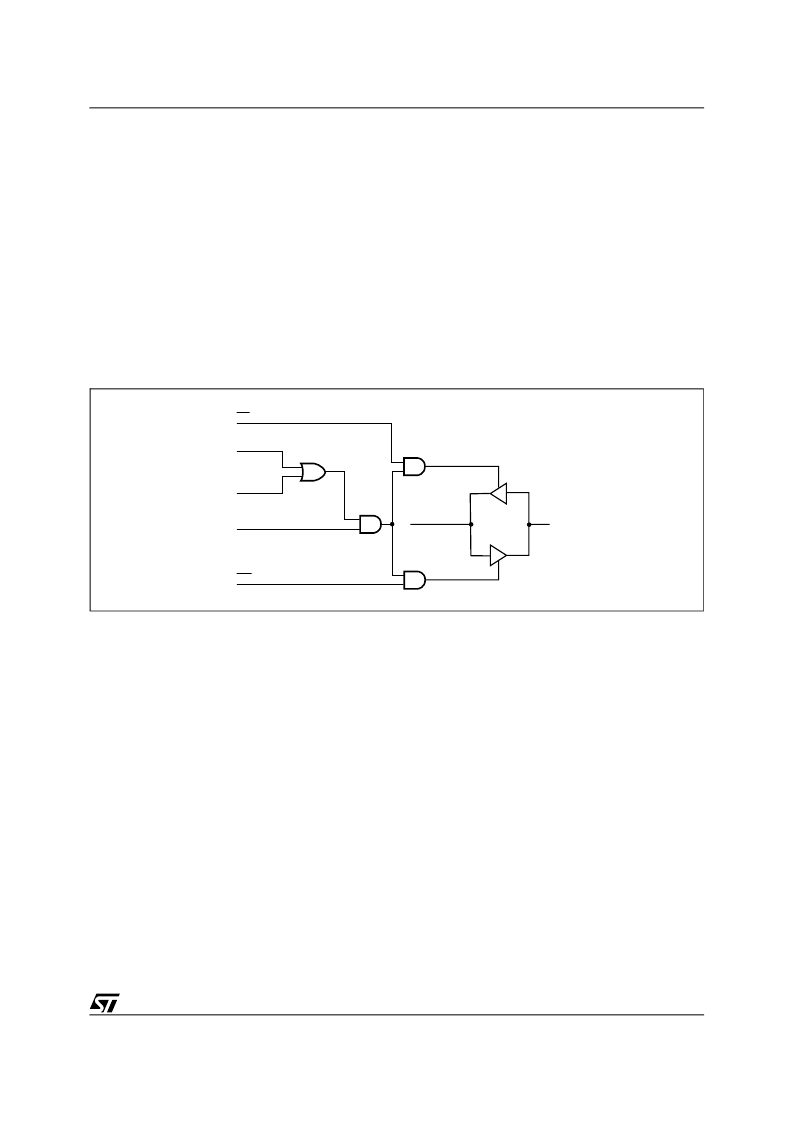

Peripheral I/O Mode

Peripheral I/O mode can be used to interface with

external peripherals. In this mode, all of Port A

serves as a tri-state, bi-directional data buffer for

the MCU. Peripheral I/O Mode is enabled by set-

ting Bit 7 of the VM Register to a ’1.’ Figure

27

shows how Port A acts as a bi-directional buffer for

the MCU data bus if Peripheral I/O Mode is en-

abled. An equation for PSEL0 and/or PSEL1 must

be written in PSDabel. The buffer is tri-stated

when PSEL0 or PSEL1 is not active.

Figure 27. Peripheral I/O Mode

RD

PSEL0

PSEL1

PSEL

VM REGISTER BIT 7

WR

PA0-PA7

D0-D7

DATA BUS

AI02886

相关PDF资料 |

PDF描述 |

|---|---|

| PSD9543V15JIT | 3.3V, Wide Bandwidth, 2-Channel, 2:1 Mux/Demux USB 2.0 Switch |

| PSD8134V15JIT | Dual SPDT for USB 2.0 HS Compliance and Flow through Pinout |

| PSD9134V15JIT | Dual SPDT for USB 2.0 HS Compliance with 8kV ESD Protection |

| PSD8334V15JIT | Dual SPDT for USB 2.0 HS Compliance with Charge-pump |

| PSD9334V15JIT | 3.3V, 2-Channel, 4:1 Mux USB 2.0 Switch |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD854F2-15J | 制造商:STMicroelectronics 功能描述:4556DIE2HR - Trays |

| PSD854F2-70J | 功能描述:CPLD - 复杂可编程逻辑器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| PSD854F2-70M | 功能描述:CPLD - 复杂可编程逻辑器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| PSD854F2-90J | 功能描述:CPLD - 复杂可编程逻辑器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| PSD854F2-90JI | 功能描述:CPLD - 复杂可编程逻辑器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。