- 您现在的位置:买卖IC网 > PDF目录376269 > PSD854590MIT (意法半导体) Flash In-System Programmable ISP Peripherals For 8-bit MCUs PDF资料下载

参数资料

| 型号: | PSD854590MIT |

| 厂商: | 意法半导体 |

| 英文描述: | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| 中文描述: | Flash在系统可编程ISP的外设的8位微控制器 |

| 文件页数: | 6/110页 |

| 文件大小: | 1737K |

| 代理商: | PSD854590MIT |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

6/110

SUMMARY DESCRIPTION

The PSD8XXFX family of memory systems for mi-

crocontrollers (MCUs) brings In-System-Program-

mability (ISP) to Flash memory and programmable

logic. The result is a simple and flexible solution for

embedded designs. PSD devices combine many

of the peripheral functions found in MCU based

applications.

Table

1

summarizes all the devices in the

PSD834F2, PSD853F2, PSD854F2.

The CPLD in the PSD devices features an opti-

mized macrocell logic architecture. The PSD mac-

rocell was created to address the unique

requirements of embedded system designs. It al-

lows direct connection between the system ad-

dress/data bus, and the internal PSD registers, to

simplify communication between the MCU and

other supporting devices.

The PSD device includes a JTAG Serial Program-

ming interface, to allow In-System Programming

(ISP) of the

entire device

. This feature reduces de-

velopment time, simplifies the manufacturing flow,

and dramatically lowers the cost of field upgrades.

Using ST’s special Fast-JTAG programming, a de-

sign can be rapidly programmed into the PSD in as

little as seven seconds.

The innovative PSD8XXFX family solves key

problems faced by designers when managing dis-

crete Flash memory devices, such as:

–

First-time In-System Programming (ISP)

–

Complex address decoding

–

Simultaneous read and write to the device.

The JTAG Serial Interface block allows In-System

Programming (ISP), and eliminates the need for

an external Boot EPROM, or an external program-

mer. To simplify Flash memory updates, program

execution is performed from a secondary Flash

memory while the primary Flash memory is being

updated. This solution avoids the complicated

hardware and software overhead necessary to im-

plement IAP.

ST makes available a software development tool,

PSDsoft Express, that generates ANSI-C compli-

ant code for use with your target MCU. This code

allows you to manipulate the non-volatile memory

(NVM) within the PSD. Code examples are also

provided for:

–

Flash memory IAP via the UART of the host

MCU

–

Memory paging to execute code across

several PSD memory pages

–

Loading, reading, and manipulation of PSD

macrocells by the MCU.

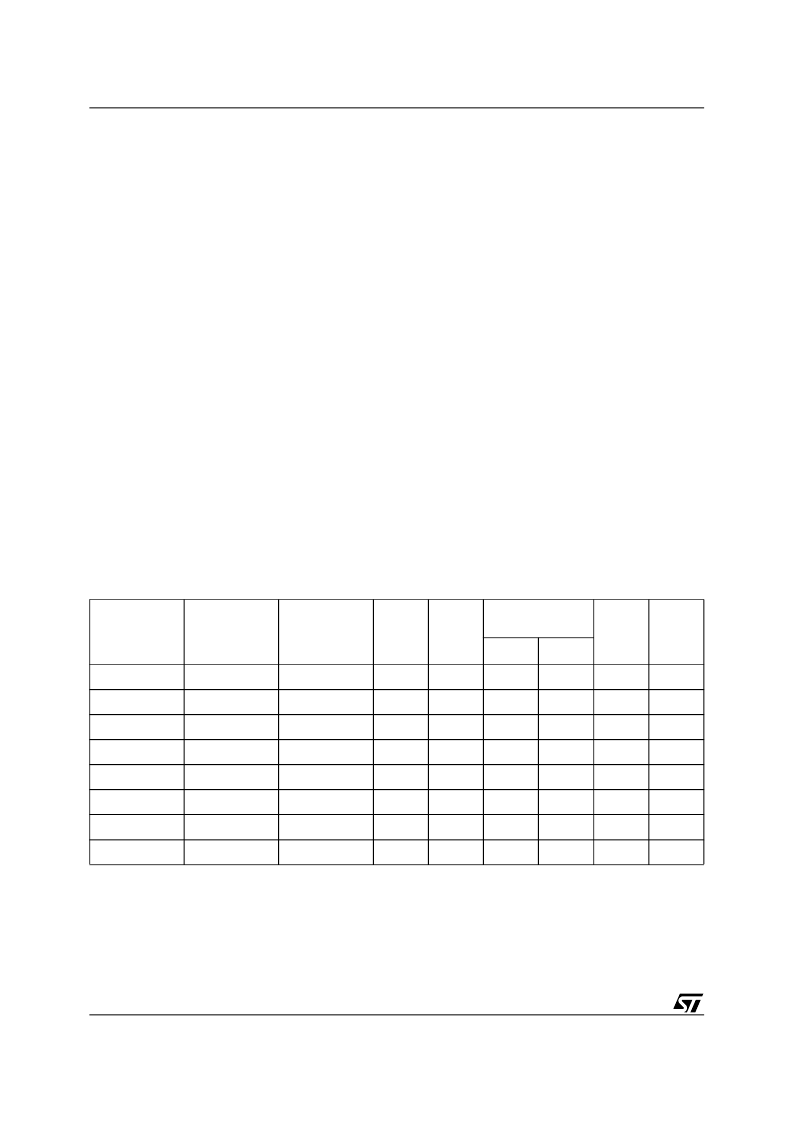

Table 1. Product Range

Note: 1. All products support: JTAG serial ISP, MCU parallel ISP, ISP Flash memory, ISP CPLD, Security features, Power Management

Unit (PMU), Automatic Power-down (APD)

2. SRAM may be backed up using an external battery.

Part Number

(1)

Primary Flash

Memory

(8 Sectors)

Secondary

Flash Memory

4 Sectors)

SRAM

(2)

I/O Ports

Number of

Macrocells

Serial

ISP

JTAG/

ISC Port

Turbo

Mode

Input

Output

PSD813F2

1 Mbit

256 Kbit

16 Kbit

27

24

16

yes

yes

PSD813F3

1 Mbit

none

16 Kbit

27

24

16

yes

yes

PSD813F4

1 Mbit

256 Kbit

none

27

24

16

yes

yes

PSD813F5

1 Mbit

none

none

27

24

16

yes

yes

PSD833F2

1 Mbit

256 Kbit

64 Kbit

27

24

16

yes

yes

PSD834F2

2 Mbit

256 Kbit

64 Kbit

27

24

16

yes

yes

PSD853F2

1 Mbit

256 Kbit

256 Kbit

27

24

16

yes

yes

PSD854F2

2 Mbit

256 Kbit

256 Kbit

27

24

16

yes

yes

相关PDF资料 |

PDF描述 |

|---|---|

| PSD854590MT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD8545V12JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD8545V12JT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD8545V12MIT | Dual 4A MOSFET Driver 8-PDIP -40 to 105 |

| PSD8545V12MT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD854F2-15J | 制造商:STMicroelectronics 功能描述:4556DIE2HR - Trays |

| PSD854F2-70J | 功能描述:CPLD - 复杂可编程逻辑器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| PSD854F2-70M | 功能描述:CPLD - 复杂可编程逻辑器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| PSD854F2-90J | 功能描述:CPLD - 复杂可编程逻辑器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| PSD854F2-90JI | 功能描述:CPLD - 复杂可编程逻辑器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。