- 您现在的位置:买卖IC网 > PDF目录368293 > PSD935F3V-A-15J (意法半导体) Configurable Memory System on a Chip for 8-Bit Microcontrollers PDF资料下载

参数资料

| 型号: | PSD935F3V-A-15J |

| 厂商: | 意法半导体 |

| 英文描述: | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| 中文描述: | 在8片位微控制器可配置存储系统 |

| 文件页数: | 51/91页 |

| 文件大小: | 488K |

| 代理商: | PSD935F3V-A-15J |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页

PSD9XX Family

PSD935G2

50

9.4.3 Port Configuration Registers (PCRs)

Each port has a set of PCRs used for configuration. The contents of the registers can be

accessed by the microcontroller through normal read/write bus cycles at the addresses

given in Table 6. The addresses in Table 6 are the offsets in hex from the base of the

CSIOP register.

The pins of a port are individually configurable and each bit in the register controls its

respective pin. For example, Bit 0 in a register refers to Bit 0 of its port. The three PCRs,

shown in Table 19, are used for setting the port configurations. The default power-up state

for each register in Table 22 is 00h.

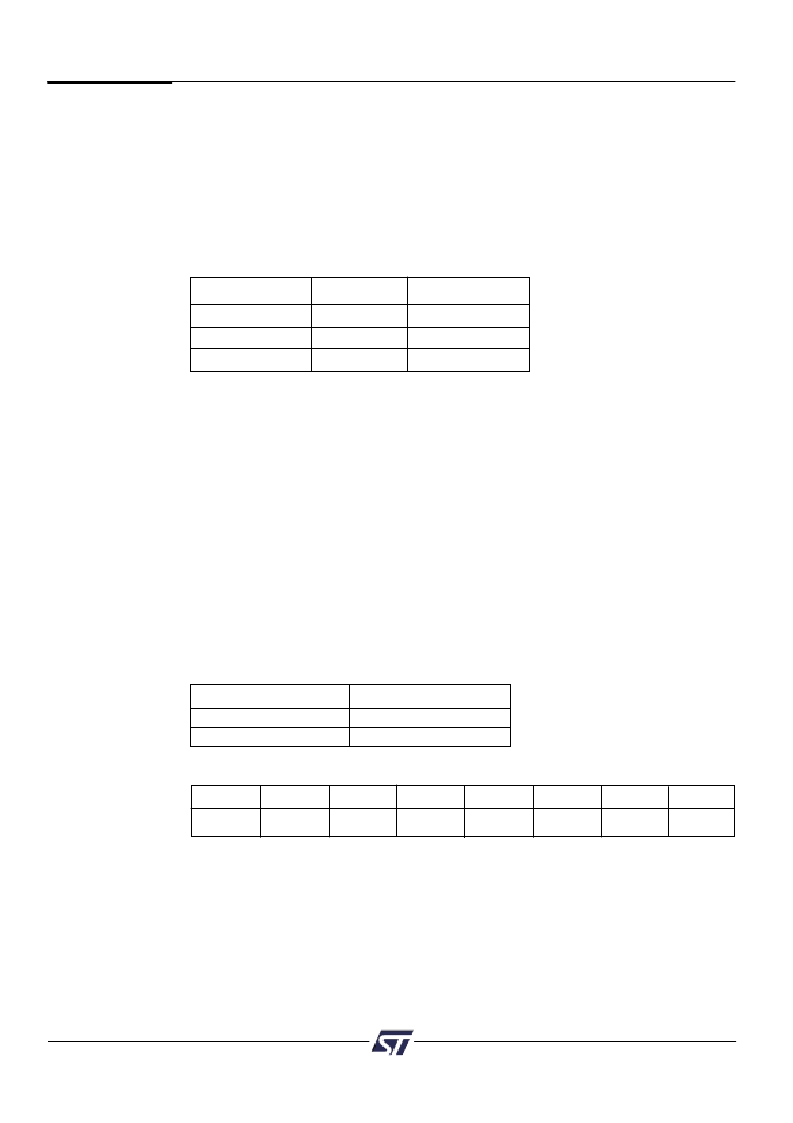

Register Name

Port

MCU Access

Control

Direction

Drive Select*

E,F,G

A,B,C,D,E,F,G

A,B,C,D,E,F,G

Write/Read

Write/Read

Write/Read

Table 19. Port Configuration Registers

*

NOTE:

See Table 22 for Drive Register bit definition.

The

PSD935G2

Functional

Blocks

(cont.)

9.4.3.1 Control Register

Any bit set to ‘0’ in the Control Register sets the corresponding Port pin to MCU I/O Mode,

and a ‘1’ sets it to Address Out Mode. The default mode is MCU I/O. Only Ports E, F and

G have an associated Control Register.

9.4.3.2 Direction Register

The Direction Register controls the direction of data flow in the I/O Ports. Any bit set to ‘1’

in the Direction Register will cause the corresponding pin to be an output, and any bit set

to ‘0’ will cause it to be an input. The default mode for all port pins is input.

Figures 21 and 23 show the Port Architecture diagrams for Ports A/B/C and E/F/G

respectively. The direction of data flow for Ports A, B, C and F are controlled by the

direction register.

An example of a configuration for a port with the three least significant bits set to output

and the remainder set to input is shown in Table 21. Since Port D only contains four pins,

the Direction Register for Port D has only the four least significant bits active.

Direction Register Bit

0

1

Port Pin Mode

Input

Output

Table 20. Port Pin Direction Control

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

0

0

0

0

1

1

1

Table 21. Port Direction Assignment Example

相关PDF资料 |

PDF描述 |

|---|---|

| PSD935F3V-A-15JI | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F3V-A-15M | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F3V-A-15MI | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F3V-A-15U | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F3V-A-15UI | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD935G2-90U | 功能描述:SPLD - 简单可编程逻辑器件 TQFP-80 5V 4M 90N RoHS:否 制造商:Texas Instruments 逻辑系列:TICPAL22V10Z 大电池数量:10 最大工作频率:66 MHz 延迟时间:25 ns 工作电源电压:4.75 V to 5.25 V 电源电流:100 uA 最大工作温度:+ 75 C 最小工作温度:0 C 安装风格:Through Hole 封装 / 箱体:DIP-24 |

| PSD935G2V-90U | 功能描述:SPLD - 简单可编程逻辑器件 U 511-PSD835G2V-90U RoHS:否 制造商:Texas Instruments 逻辑系列:TICPAL22V10Z 大电池数量:10 最大工作频率:66 MHz 延迟时间:25 ns 工作电源电压:4.75 V to 5.25 V 电源电流:100 uA 最大工作温度:+ 75 C 最小工作温度:0 C 安装风格:Through Hole 封装 / 箱体:DIP-24 |

| PSD954F2-90J | 功能描述:SPLD - 简单可编程逻辑器件 U 511-PSD854F2-90J RoHS:否 制造商:Texas Instruments 逻辑系列:TICPAL22V10Z 大电池数量:10 最大工作频率:66 MHz 延迟时间:25 ns 工作电源电压:4.75 V to 5.25 V 电源电流:100 uA 最大工作温度:+ 75 C 最小工作温度:0 C 安装风格:Through Hole 封装 / 箱体:DIP-24 |

| PSD954F2-90M | 功能描述:SPLD - 简单可编程逻辑器件 U 511-PSD854F2-90M RoHS:否 制造商:Texas Instruments 逻辑系列:TICPAL22V10Z 大电池数量:10 最大工作频率:66 MHz 延迟时间:25 ns 工作电源电压:4.75 V to 5.25 V 电源电流:100 uA 最大工作温度:+ 75 C 最小工作温度:0 C 安装风格:Through Hole 封装 / 箱体:DIP-24 |

| PSD954F2V-90J | 功能描述:SPLD - 简单可编程逻辑器件 5.0V 2M 90ns RoHS:否 制造商:Texas Instruments 逻辑系列:TICPAL22V10Z 大电池数量:10 最大工作频率:66 MHz 延迟时间:25 ns 工作电源电压:4.75 V to 5.25 V 电源电流:100 uA 最大工作温度:+ 75 C 最小工作温度:0 C 安装风格:Through Hole 封装 / 箱体:DIP-24 |

发布紧急采购,3分钟左右您将得到回复。