- 您现在的位置:买卖IC网 > PDF目录98065 > PTH08000WAZT (TEXAS INSTRUMENTS INC) 1-OUTPUT DC-DC REG PWR SUPPLY MODULE PDF资料下载

参数资料

| 型号: | PTH08000WAZT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 电源模块 |

| 英文描述: | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| 封装: | ROHS COMPLIANT, DIP-6 |

| 文件页数: | 14/20页 |

| 文件大小: | 661K |

| 代理商: | PTH08000WAZT |

www.ti.com

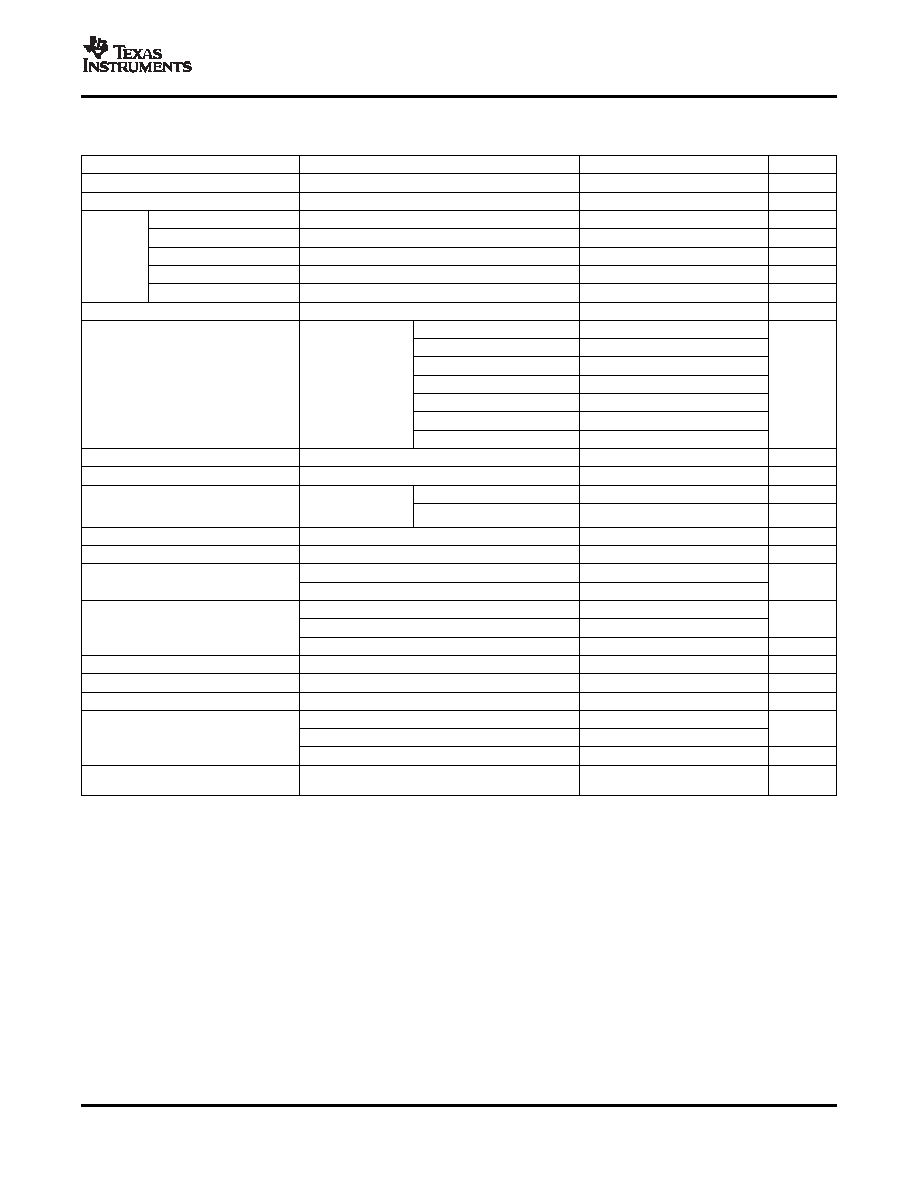

ELECTRICAL CHARACTERISTICS

SLTS248B – JUNE 2005 – REVISED FEBRUARY 2008

at 25

°C free-air temperature, V

I = 12 V, VO = 3.3 V, IO = IOmax, CI = 100 F (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

IO

Output current

TA = 85°C, natural convection airflow

0

2.25

A

VI

Input voltage range

Over IO range

4.5 (1)

14

V

Set-point voltage tolerance

TA = 25°C

2 (2)

%

Temperature variation

-40

°C ≤ T

A ≤ 85°C

0.5

%VO

VO

Line regulation

Over VI range

7

mV

Load regulation

Over IO range

0.13

%VO

Total output voltage variation

Includes set-point, line, load, -40

°C ≤ T

A ≤ 85°C

3 (2)

%VO

V(ADJ)

Output Voltage Adjust Range

Over IO range

0.9

5.5

V

RSET = 346 , VO = 5 V

93.5%

RSET = 1.87 k, VO = 3.3 V

92%

RSET = 3.74 k, VO = 2.5 V

90.5%

TA = 25°C,

η

Efficiency

RSET = 6.19 k, VO = 2 V

89.5%

IO = 2 A

RSET = 8.06 k, VO = 1.8 V

88%

RSET = 13 k, VO = 1.5 V

86.5%

RSET = 27.4 k, VO = 1.2 V

84.5%

Output voltage ripple

20-MHz bandwidth

40

mVPP

Overcurrent threshold

Reset, followed by autorecovery

3.5

A

CO = 100 F, 1 A/s

Recovery time

50

s

Transient response

load step from 50% to

VO over/undershoot

100

mV

100% IOmax

IIL track

Track input current (pin 2)

Pin to GND

–130

A

dVtrack/dt

Track slew rate capability

CO ≤ CO(max)

1

V/ms

VI = increasing

4.35

4.5

UVLO

Undervoltage lockout

V

VI = decreasing

3.6

4

Input high voltage (VIH)

Open (3)

V

Inhibit control (pin 4)

Input low voltage (VIL)

–0.2

0.5

Input low current (IIL)

–5

A

II (stby)

Input standby current

Pins 5 and 2 connected

1

mA

fS

Switching frequency

Over VI and IO ranges

300

kHz

External input capacitance

Electrolytic type (CI)

100 (4)

F

Ceramic type (CO)

220

F

External output capacitance

Nonceramic type (CO)

100 (5)

330 (6)

Equivalent series resistance (nonceramic)

10 (7)

m

Per Telcordia SR-332, 50% stress,

MTBF

Calculated reliability

10.3

106 Hr

TA = 40°C, ground benign

(1)

The minimum input voltage is 4.5 V or (VO + 1.1) V, whichever is greater.

(2)

The set-point voltage tolerance is affected by the tolerance and stability of RSET. The stated limit is unconditionally met if RSET has a

tolerance of 1% with 100 ppm/

°C or better temperature stability.

(3)

This control pin has an internal pull-up to 3 V (TYP). Do not place an external pull-up on this pin. If it is left open-circuit, the module

operates when input power is applied. A small, low-leakage (< 100 nA) MOSFET is recommended for control. See the Application

section for further guidance.

(4)

An external 100-F electrolytic capacitor is required across the input (VI and GND) for proper operation. Locate the capacitor close to

the module.

(5)

An external output capacitor is not required for proper operation. Adding 100 F of distributed capacitance at the load improves the

transient response.

(6)

This is the calculated maximum capacitance. The minimum ESR limitation often results in a lower value. See the capacitor application

information for further guidance.

(7)

This is the minimum ESR for all the electrolytic (nonceramic) capacitance. Use 14 m

as the minimum when calculating the total

equivalent series resistance (ESR) using the maximum ESR values specified by the capacitor manufacturer.

Copyright 2005–2008, Texas Instruments Incorporated

3

Product Folder Link(s) :PTH08000W

相关PDF资料 |

PDF描述 |

|---|---|

| PTH08T240FAS | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| PTH08T240FAST | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| PTH08T240FAD | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| PTH12010LAZT | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| PTH12010LAST | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PTH08080W | 制造商:TI 制造商全称:Texas Instruments 功能描述:2.25-A, WIDE-INPUT ADJUSTABLE SWITCHING REGULATOR |

| PTH08080WAD | 功能描述:DC/DC转换器 2.25A Wide Input/ Out Adj Mini Pwr Mdl RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸: |

| PTH08080WAH | 功能描述:DC/DC转换器 2.25A Wide Input/ Out Adj Mini Pwr Mdl RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸: |

| PTH08080WAS | 功能描述:DC/DC转换器 2.25A Wide Input/ Out Adj Mini Pwr Mdl RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸: |

| PTH08080WAST | 功能描述:DC/DC转换器 2.25A Wide Input/ Out Adj Mini Pwr Mdl RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸: |

发布紧急采购,3分钟左右您将得到回复。