- 您现在的位置:买卖IC网 > PDF目录368401 > PZ5032-6A44 Electrically-Erasable Complex PLD PDF资料下载

参数资料

| 型号: | PZ5032-6A44 |

| 英文描述: | Electrically-Erasable Complex PLD |

| 中文描述: | 电可擦除复杂可编程逻辑器件 |

| 文件页数: | 5/14页 |

| 文件大小: | 107K |

| 代理商: | PZ5032-6A44 |

Philips Semiconductors

Product specification

PZ5032

32 macrocell CPLD

1997 Feb 20

5

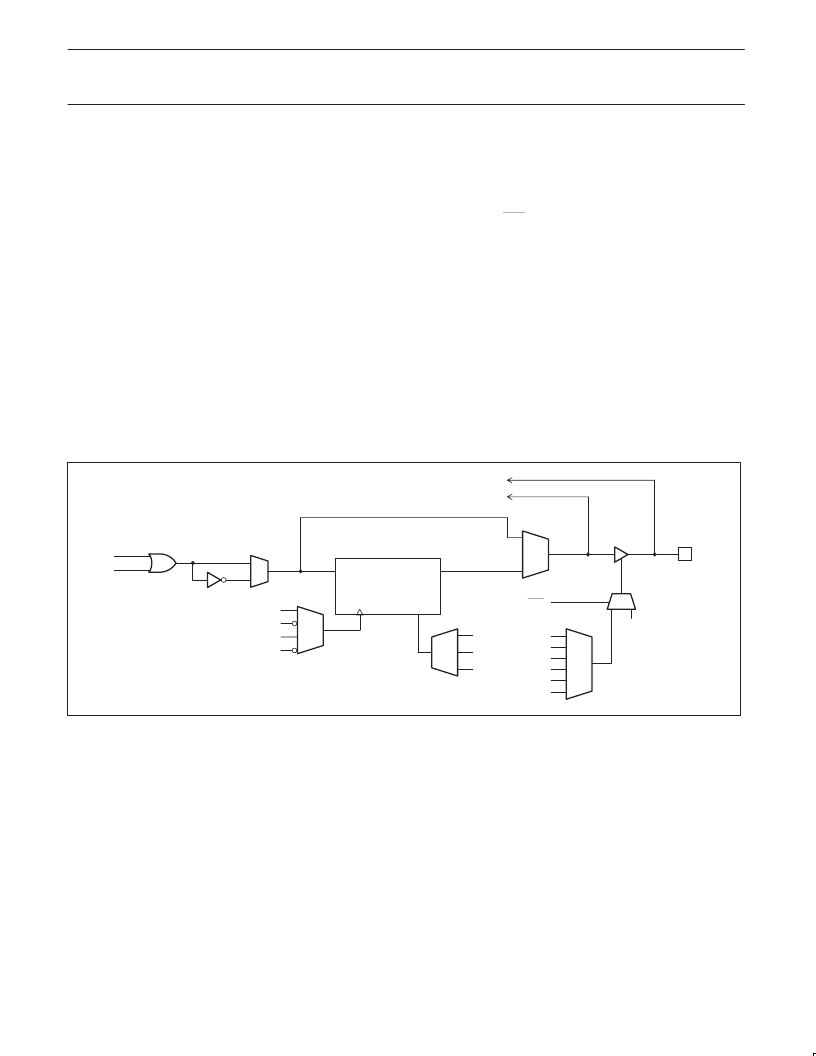

Macrocell Architecture

Figure 3 shows the architecture of the macrocell used in the

CoolRunner

family. The macrocell consists of a flip-flop that can be

configured as either a D or T type. A D-type flip-flop is generally

more useful for implementing state machines and data buffering. A

T-type flip-flop is generally more useful in implementing counters. All

CoolRunner

family members provide both synchronous and

asynchronous clocking and provide the ability to clock off either the

falling or rising edges of these clocks. These devices are designed

such that the skew between the rising and falling edges of a clock

are minimized for clocking integrity. There are 2 clocks (CLK0 and

CLK1) available on the PZ5032 device. Clock 0 (CLK0) is

designated as the “synchronous” clock and must be driven by an

external source. Clock 1 (CLK1) can either be used as a

synchronous clock (driven by an external source) or as an

asynchronous clock (driven by a macrocell equation).

Two of the control terms (CT0 and CT1) are used to control the

Preset/Reset of the macrocell’s flip-flop. The Preset/Reset feature

for each macrocell can also be disabled. Note that the Power-on

Reset leaves all macrocells in the “zero” state when power is

properly applied. The other 4 control terms (CT2–CT5) can be used

to control the Output Enable of the macrocell’s output buffers. The

reason there are as many control terms dedicated for the Output

Enable of the macrocell is to insure that all CoolRunner

devices

are PCI compliant. The macrocell’s output buffers can also be

always enabled or disabled. All CoolRunner

devices also provide a

Global Tri-State (GTS) pin, which, when pulled Low, will 3-State all

the outputs of the device. This pin is provided to support “In-Circuit

Testing” or “Bed-of-Nails Testing”.

There are two feedback paths to the ZIA: one from the macrocell,

and one from the I/O pin. The ZIA feedback path before the output

buffer is the macrocell feedback path, while the ZIA feedback path

after the output buffer is the I/O pin ZIA path. When the macrocell is

used as an output, the output buffer is enabled, and the macrocell

feedback path can be used to feedback the logic implemented in the

macrocell. When the I/O pin is used as an input, the output buffer

will be 3-Stated and the input signal will be fed into the ZIA via the

I/O feedback path, and the logic implemented in the buried

macrocell can be fed back to the ZIA via the macrocell feedback

path. It should be noted that unused inputs or I/Os should be

properly terminated.

CT2

CT3

CT4

CT5

V

CC

GND

INIT

(P or R)

D/T

Q

SP00440

CLK0

CLK0

CLK1

CLK1

TO ZIA

GND

CT0

CT1

GND

GTS

Figure 3.

PZ5032 Macrocell Architecture

相关PDF资料 |

PDF描述 |

|---|---|

| PZ5032-6BC | Electrically-Erasable Complex PLD |

| PZ5032-6BC-S | Electrically-Erasable Complex PLD |

| PZ5032-7(TBD) | ASIC |

| PZ5032-7A44 | Electrically-Erasable Complex PLD |

| PZ5032-7BC | Electrically-Erasable Complex PLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PZ5128-S7BP | 制造商: 功能描述: 制造商:undefined 功能描述: |

| PZ-5-3 | 制造商:WM BERG 功能描述: |

| PZ5CG | 制造商:未知厂家 制造商全称:未知厂家 功能描述:0.5 KV ISOLATED 0.75 W REGULATED SINGLE OUTPUT SIP7 |

| PZ5CG-0505E | 制造商:未知厂家 制造商全称:未知厂家 功能描述:0.5 KV ISOLATED 0.75 W REGULATED SINGLE OUTPUT SIP7 |

| PZ5CG-0512E | 制造商:未知厂家 制造商全称:未知厂家 功能描述:0.5 KV ISOLATED 0.75 W REGULATED SINGLE OUTPUT SIP7 |

发布紧急采购,3分钟左右您将得到回复。