- 您现在的位置:买卖IC网 > PDF目录368401 > PZ5032I7BC Electrically-Erasable Complex PLD PDF资料下载

参数资料

| 型号: | PZ5032I7BC |

| 英文描述: | Electrically-Erasable Complex PLD |

| 中文描述: | 电可擦除复杂可编程逻辑器件 |

| 文件页数: | 11/14页 |

| 文件大小: | 107K |

| 代理商: | PZ5032I7BC |

Philips Semiconductors

Product specification

PZ5032

32 macrocell CPLD

1997 Feb 20

11

PIN DESCRIPTIONS

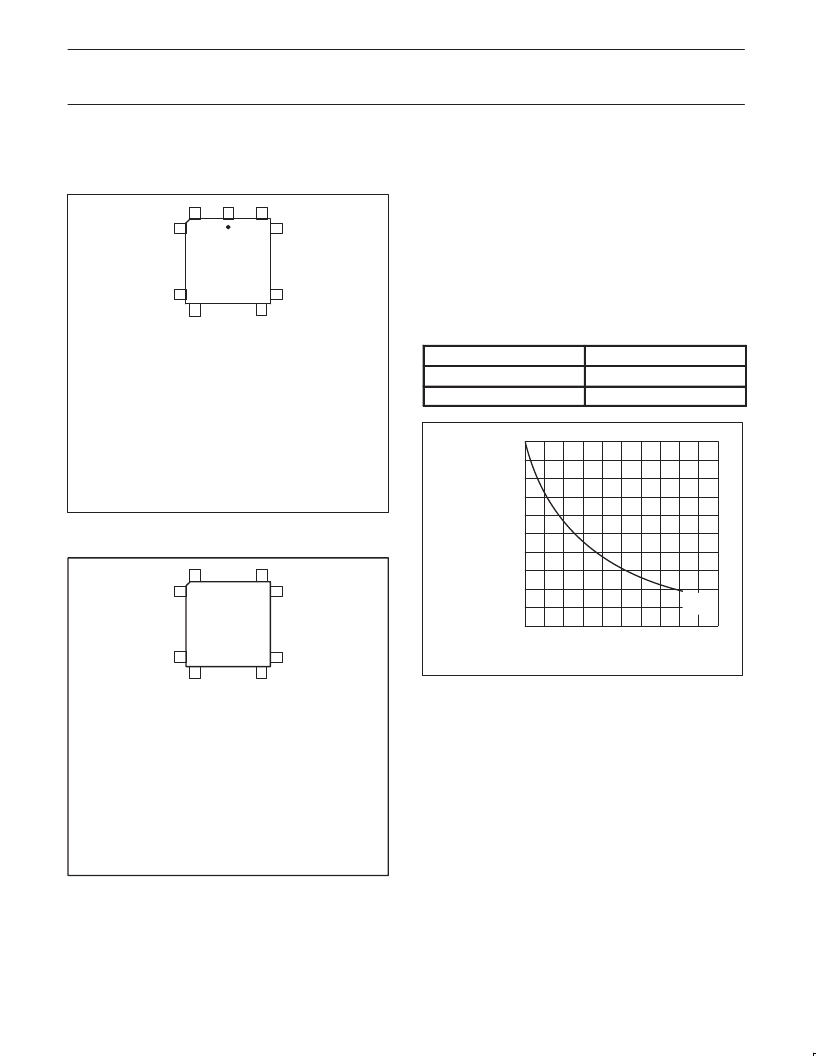

PZ5032 – 44-Pin Plastic Leaded Chip Carrier

1

6

7

17

18

28

29

39

40

Pin

Function

IN1

IN3

V

DD

I/O–A0–CK1

I/O–A1

I/O–A2

I/O–A3

I/O–A4

I/O–A5

GND

I/O–A6

I/O–A7

I/O–A8

I/O–A9

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Pin

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

Function

I/O–A10

I/O–A11

I/O–A12

I/O–A13

I/O–A14

I/O–A15

GND

V

DD

I/O–B15

I/O–B14

I/O–B13

I/O–B12

I/O–B11

I/O–B10

GND

Pin

31

32

33

34

35

36

37

38

39

40

41

42

43

44

Function

I/O–B9

I/O–B8

I/O–B7

I/O–B6

V

DD

I/O–B5

I/O–B4

I/O–B3

I/O–B2

I/O–B1

I/O–B0

GND

IN0–CK0

IN2–gtsn

PLCC

SP00420

PZ5032 – 44-Pin Thin Quad Flat Package

44

1

11

12

22

23

33

34

Pin

Function

I/O–A3

I/O–A4

I/O–A5

GND

I/O–A6

I/O–A7

I/O–A8

I/O–A9

V

DD

I/O–A10

I/O–A11

I/O–A12

I/O–A13

I/O–A14

I/O–A15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Pin

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

Function

GND

V

DD

I/O–B15

I/O–B14

I/O–B13

I/O–B12

I/O–B11

I/O–B10

GND

I/O–B9

I/O–B8

I/O–B7

I/O–B6

V

DD

I/O–B5

Pin

31

32

33

34

35

36

37

38

39

40

41

42

43

44

Function

I/O–B4

I/O–B3

I/O–B2

I/O–B1

I/O–B0

GND

IN0/CK0

IN2–gtsn

IN1

IN3

V

DD

I/O–A0–CK1

I/O–A1

I/O–A2

TQFP

SP00433

Package Thermal Characteristics

Philips Semiconductors uses the Temperature Sensitive Parameter

(TSP) method to test thermal resistance. This method meets

Mil-Std-883C Method 1012.1 and is described in Philips 1995 IC

Package Databook Thermal resistance varies slightly as a function

of input power. As input power increases, thermal resistance

changes approximately 5% for a 100% change in power.

Figure 7 is a derating curve for the change in

Θ

JA

with airflow based

on wind tunnel measurements. It should be noted that the wind flow

dynamics are more complex and turbulent in actual applications

than in a wind tunnel. Also, the test boards used in the wind tunnel

contribute significantly to forced convection heat transfer, and may

not be similar to the actual circuit board, especially in size.

Package

Θ

JA

44-pin PLCC

49.8

°

C/W

44-pin TQFP

66.3

°

C/W

0

10

20

30

40

50

0

1

2

3

4

5

PERCENTAGE

REDUCTION IN

Θ

JA

(%)

AIR FLOW (m/s)

PLCC/

QFP

SP00419A

Figure 7.

Average Effect of Airflow on

Θ

JA

相关PDF资料 |

PDF描述 |

|---|---|

| PZ5032I7BC-S | Electrically-Erasable Complex PLD |

| PZ5128 | 128 macrocell CPLD |

| PZ5128IS10BB1 | Electrically-Erasable Complex PLD |

| PZ5128IS10BB1-S | Electrically-Erasable Complex PLD |

| PZ5128IS10BB2 | Electrically-Erasable Complex PLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PZ5128-S7BP | 制造商: 功能描述: 制造商:undefined 功能描述: |

| PZ-5-3 | 制造商:WM BERG 功能描述: |

| PZ5CG | 制造商:未知厂家 制造商全称:未知厂家 功能描述:0.5 KV ISOLATED 0.75 W REGULATED SINGLE OUTPUT SIP7 |

| PZ5CG-0505E | 制造商:未知厂家 制造商全称:未知厂家 功能描述:0.5 KV ISOLATED 0.75 W REGULATED SINGLE OUTPUT SIP7 |

| PZ5CG-0512E | 制造商:未知厂家 制造商全称:未知厂家 功能描述:0.5 KV ISOLATED 0.75 W REGULATED SINGLE OUTPUT SIP7 |

发布紧急采购,3分钟左右您将得到回复。