- 您现在的位置:买卖IC网 > PDF目录296936 > QL2003-XPF100I Field Programmable Gate Array (FPGA) PDF资料下载

参数资料

| 型号: | QL2003-XPF100I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 现场可编程门阵列(FPGA) |

| 文件页数: | 10/10页 |

| 文件大小: | 182K |

| 代理商: | QL2003-XPF100I |

QL2003

3-13

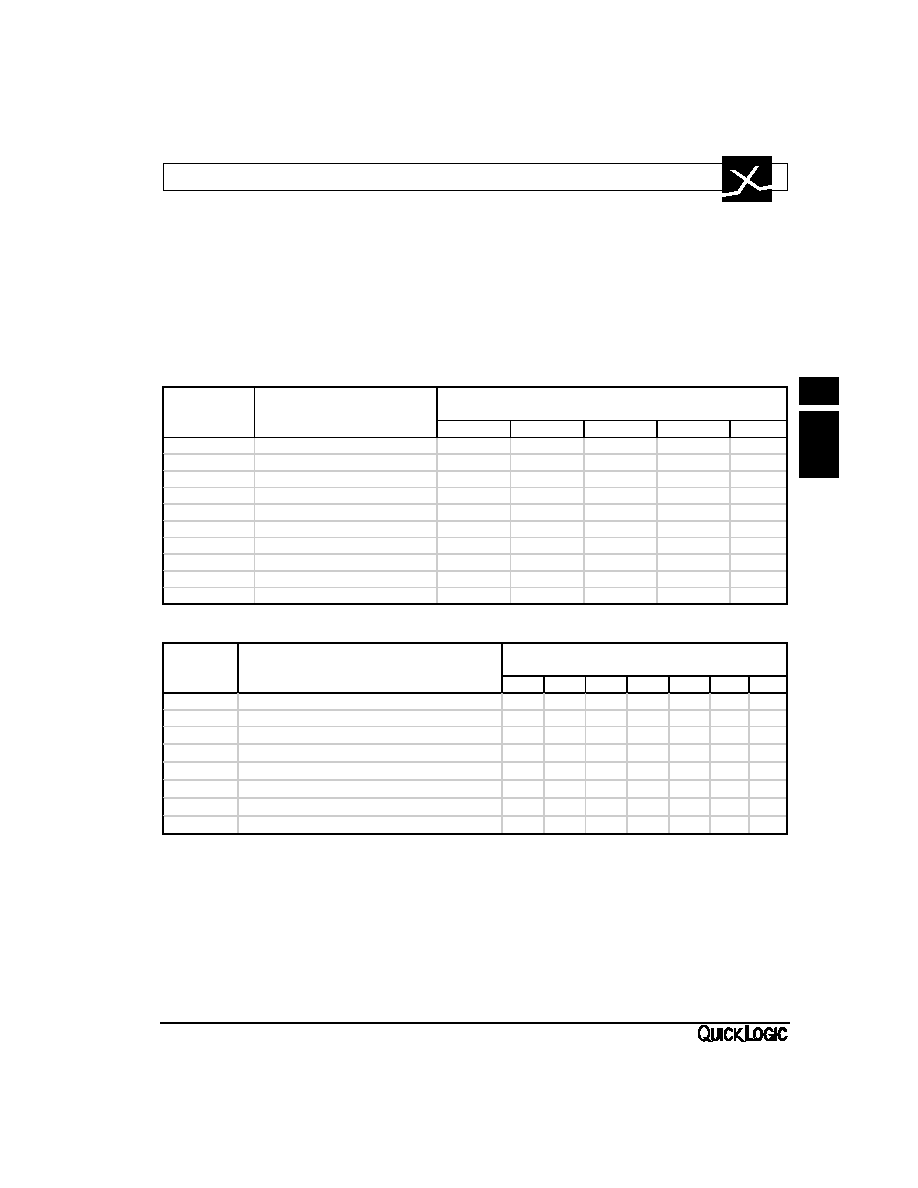

AC CHARACTERISTICS at VCC = 5V, TA = 25

°°C (K = 1.00)

Propagation delays depend on routing, fanout, load capacitance, supply voltage, junction temperature,

and process variation. The AC Characteristics are a design guide to provide initial timing estimates at

nominal conditions. Worst case estimates are obtained when nominal propagation delays are multiplied

by the appropriate Delay Factor, K, as specified in the Delay Factor table (Operating Range). The

QuickChip/QuickTools/QuickWorks software incorporates data sheet AC Characteristics into the

design database for precise path analysis or simulation results following place and route.

Logic Cells

Input-Only Cells

Symbol

Parameter

Propagation Delays (ns)

Fanout [8]

1234

8

12

24

tIN

High Drive Input Delay

2.5

2.6

2.7

3.5

4.6

5.8

tINI

High Drive Input, Inverting Delay

2.6

2.7

2.8

3.6

4.7

5.9

tISU

Input Register Set-Up Time

4.8

tIH

Input Register Hold Time

0.0

tlCLK

Input Register Clock To Q

0.9

1.0

1.1

1.9

3.0

4.2

tlRST

Input Register Reset Delay

0.8

0.9

1.0

1.8

2.9

4.1

tlESU

Input Register clock Enable Set-Up Time

4.1

tlEH

Input Register Clock Enable Hold Time

0.0

Notes:

[8]

Stated timing for worst case Propagation Delay over process variation at VCC=5.0V and TA=25

°C.

Multiply by the appropriate Delay Factor, K, for speed grade, voltage and temperature settings as

specified in the Operating Range.

[9]

These limits are derived from a representative selection of the slowest paths through the pASIC 2 logic

cell including typical net delays. Worst case delay values for specific paths should be determined from

timing analysis of your particular design.

Symbol

Parameter

Propagation Delays (ns)

Fanout [8]

12

34

8

tPD

Combinatorial Delay [9]

1.4

1.7

2.0

2.3

3.5

tSU

Setup Time [9]

1.8

tH

Hold Time

0.0

tCLK

Clock to Q Delay

0.8

1.1

1.4

1.7

2.9

tCWHI

Clock High Time

2.0

tCWLO

Clock Low Time

2.0

tSET

Set Delay

1.4

1.7

2.0

2.3

3.5

tRESET

Reset Delay

1.2

1.5

1.8

2.1

3.3

tSW

Set Width

1.9

tRW

Reset Width

1.8

pAS

IC

2

3

相关PDF资料 |

PDF描述 |

|---|---|

| QL2003-XPF144C | Field Programmable Gate Array (FPGA) |

| QL2003-XPF144I | Field Programmable Gate Array (FPGA) |

| QL2003-XPL84C | Field Programmable Gate Array (FPGA) |

| QL2003-XPL84I | Field Programmable Gate Array (FPGA) |

| QL2005-0PF144C | Field Programmable Gate Array (FPGA) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL2003-XPF144C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| QL2003-XPF144I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| QL2003-XPL84C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3.3V and 5.0V pASIC-R 2 FPGA Combining Speed, Density, Low Cost and Flexibility |

| QL2003-XPL84I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3.3V and 5.0V pASIC-R 2 FPGA Combining Speed, Density, Low Cost and Flexibility |

| QL2005-0PF144C | 制造商:QuickLogic Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。