- 您现在的位置:买卖IC网 > PDF目录361292 > QL5064-33BPB484C BUS CONTROLLER PDF资料下载

参数资料

| 型号: | QL5064-33BPB484C |

| 英文描述: | BUS CONTROLLER |

| 中文描述: | 总线控制器 |

| 文件页数: | 6/37页 |

| 文件大小: | 806K |

| 代理商: | QL5064-33BPB484C |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

QL5064 QuickPCI Data Sheet

5.0 DMA Feature Overview

Each Master-mode FIFO has its own DMA controller to support maximum data throughput. Combining

one Initiator-Mode Transmit FIFO with one Initiator-Mode Receive FIFO also supports DMA Chaining.

This unique and flexible DMA chaining mode permits a 'linked-list' of transfers to be completed by the

DMA controller without software or processor intervention.

DMA Registers are accessible by the FPGA (back-end interface), as well as the PCI bus.

DMA Chaining descriptors are made of 4 64-bit Quad-Words, or 32 bytes of data per descriptor. Each

descriptor defines a DMA transaction (memory start location, size, read/write) as well as 88 bits of user-

defined information (such as a descriptor identifier, or back-end address).

DMA Chaining is a powerful DMA feature, allowing the QL5064 device to drive continuous pre-defined

DMA transactions with no processor or software interaction.

Single PCI Access (SPCI) reads and writes are supported for single quad-word transfers that do not

require FIFOs. SPCI supports IO reads and writes, configuration reads and writes, special cycles,

interrupt acknowledge cycles, as well as standard memory read/write transactions.

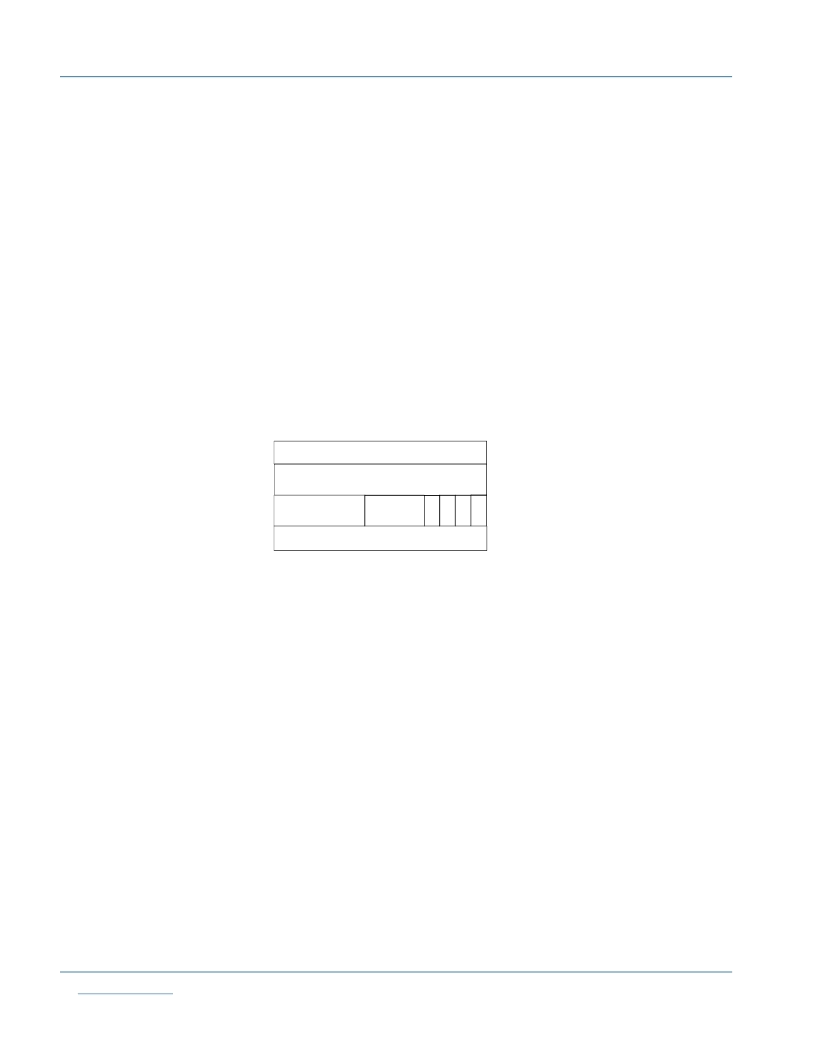

Figure 3: DMA Chaining Descriptor

User Defined (63:0)

(local address)

First PCI Address

Transfer Count (bytes)

(31:0)

User Defined

(23:0)

Next Descriptor Pointer Address (63:0)

63

0 Offset

0 x

00

0 x

08

0 x

10

0 x

18

R

I

W

C

O

E

7

0

相关PDF资料 |

PDF描述 |

|---|---|

| QL5064-33BPB484I | BUS CONTROLLER |

| QL5064-66APB456C | BUS CONTROLLER |

| QL5064-66APB456I | BUS CONTROLLER |

| QL5064-66APB484C | BUS CONTROLLER |

| QL5064-66APB484I | BUS CONTROLLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL5064-66APS484C-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66APS484I-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66BPS484C-5725 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484C-5616 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484I-5612 | 制造商:QuickLogic Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。