- 您现在的位置:买卖IC网 > PDF目录361292 > QL5064-66APB456C BUS CONTROLLER PDF资料下载

参数资料

| 型号: | QL5064-66APB456C |

| 英文描述: | BUS CONTROLLER |

| 中文描述: | 总线控制器 |

| 文件页数: | 17/37页 |

| 文件大小: | 806K |

| 代理商: | QL5064-66APB456C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

QL5064 QuickPCI Data Sheet Rev D

17

QL5064 QuickPCI Data Sheet

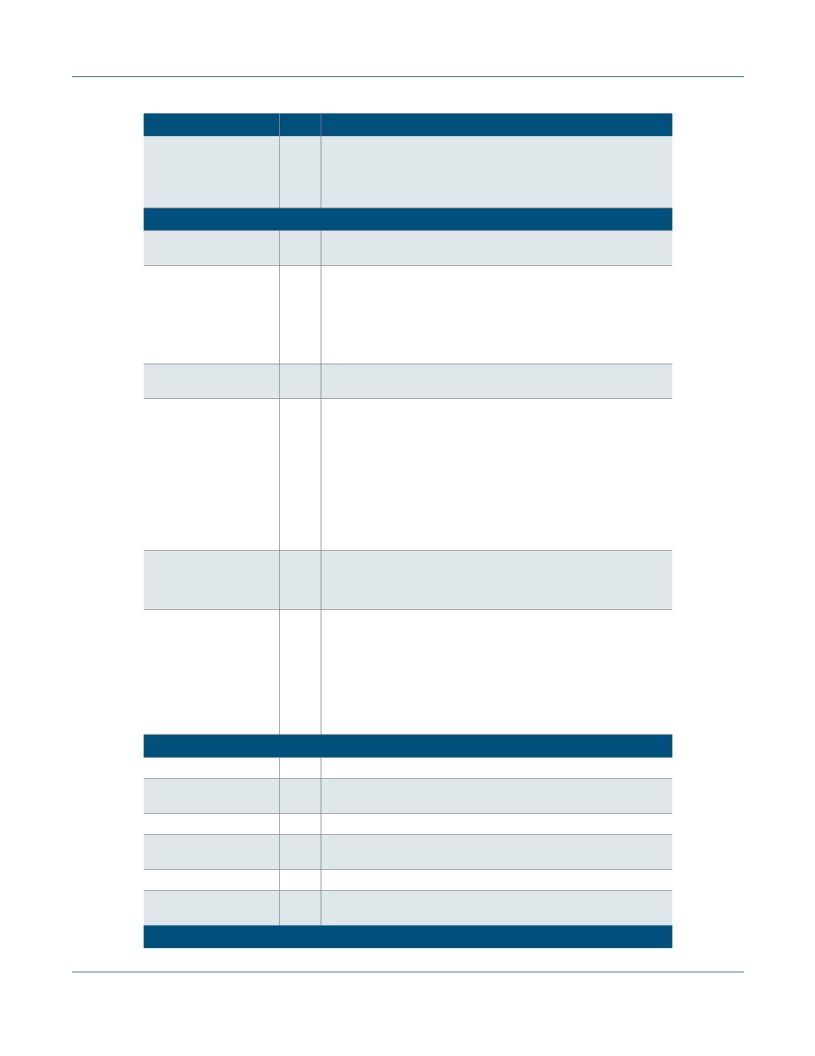

addr_select

O

Selects which half of the 64-bit PCI address for a target transaction is

placed on the user_addr [32:0] bus.

0 - [35:3]

1 - 00000. [63:36]

DataIN Bus - (PCI - FPGA)

data_IN [63:0]

I

Active High. A 64-bit bus connecting to the FIFO’s. Used by the FPGA to

obtain data being transferred from the PCI bus to the FPGA.

dataIN_src_sel[1:0]

O

Active High. Data source select signals determines which FIFO is

connected to the

data

_in bus:

00 Receive FIFO0

01 Receive FIFO1

10 Target Write post FIFO

11 Not defined (returns 0)

dataIN_cs

O

Active High. Chip select for read operations on the data_in bus. When

active, advances the pointer for the FIFO selected by dataIN_src_sel[1:0]

dataIN_BE[7:0]

I

Active High. Indicates which byte lane is active for the current transfer

occurring on dataIN[63:0]

dataIN_BE[7] dataIN[63:56]

dataIN_BE[6] dataIN[55:48]

dataIN_BE[5] dataIN[47:40]

dataIN_BE[4] dataIN[39:32]

dataIN_BE[3] dataIN[31:24]

dataIN_BE[2] dataIN[23:16]

dataIN_BE[1] dataIN[15:08]

dataIN_BE[0] dataIN[07:00]

dataIN_bytesel[2:0]

dataIN_BE[7:0] are shifted along with the data.

It is a number of bytes to barrel shift the 64-bit dataIN bus and the

dataIN_BE bus.

dataIN_byteID[1:0]

I

Active High. Tag bits for the DMA chain descriptor pointer. When active,

indicates that chain descriptor information is available at the output of

Receive FIFO0.

dataIN_byteID[1:0]

00 normal data

01 Descriptor dword 0 (PCI starting address)

10 Descriptor dword 1 (user defined)

11 Descriptor dword 2 (transfer count, et al.)

FIFO Status Signals

rcv0_fifo_ef

I

Active High. Receive FIFO0 is empty

rcv0_fifo_prog_empty_flag

I

Active High. Receive FIFO0 contains a number of entries less than or

equal to the threshold set in register 0x68, bits 37:32

rcv1_fifo_ef

I

Active High. Receive FIFO1 is empty.

rcv1_fifo_prog_empty_flag

I

Active High. Receive FIFO 1 contains a number of entries less than or

equal to the threshold set in register 0x68, bits 45:40.

xmt0_fifo_ff

I

Active High. Transmit FIFO0 is full.

xmt0_fifo_prog_full_flag

I

Active High. Transmit FIFO0 contains a number of entries greater than or

equal to the threshold set in register 0x68, bits 53:48.

Table 1: PCI Back-End Interface Signals (Continued)

Symbol

I/O

Description

(Sheet 2 of 4)

相关PDF资料 |

PDF描述 |

|---|---|

| QL5064-66APB456I | BUS CONTROLLER |

| QL5064-66APB484C | BUS CONTROLLER |

| QL5064-66APB484I | BUS CONTROLLER |

| QL5064-66BPB456C | BUS CONTROLLER |

| QL5064-66BPB456I | BUS CONTROLLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL5064-66APS484C-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66APS484I-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66BPS484C-5725 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484C-5616 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484I-5612 | 制造商:QuickLogic Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。