- 您现在的位置:买卖IC网 > PDF目录380637 > R1Q3A3618ABG-33R (Renesas Technology Corp.) 36-Mbit QDR™II SRAM 4-word Burst PDF资料下载

参数资料

| 型号: | R1Q3A3618ABG-33R |

| 厂商: | Renesas Technology Corp. |

| 英文描述: | 36-Mbit QDR™II SRAM 4-word Burst |

| 文件页数: | 17/26页 |

| 文件大小: | 407K |

| 代理商: | R1Q3A3618ABG-33R |

R1Q3A3636/R1Q3A3618/R1Q3A3609

JTAG Specification

These products support a limited set of JTAG functions as in IEEE standard 1149.1.

Disabling the Test Access Port

It is possible to use this device without utilizing the TAP. To disable the TAP controller without interfering with normal

operation of the device, TCK must be tied to V

to preclude mid level inputs. TDI and TMS are designed so an

undriven input will produce a response identical to the application of a logic 1,and may be left unconnected. But they

may also be tied to V

DD

through a 1k

resistor.TDO should be left unconnected.

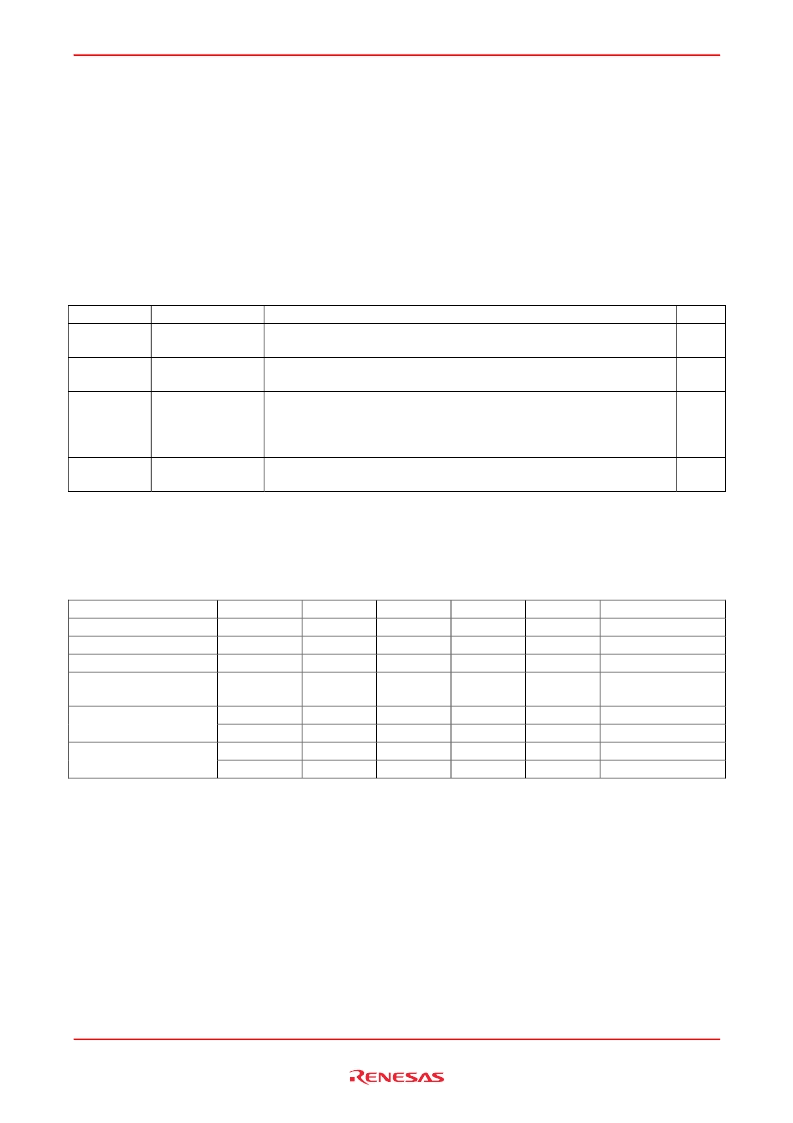

Test Access Port (TAP) Pins

Symbol I/O

TCK

Pin assignments

2R

Description

Notes

Test clock input. All inputs are captured on the rising edge of TCK and all

outputs propagate from the falling edge of TCK.

Test mode select. This is the command input for the TAP controller state

machine.

Test data input. This is the input side of the serial registers placed between

TDI and TDO. The register placed between TDI and TDO is determined by

the state of the TAP controller state machine and the instruction that is

currently loaded in the TAP instruction.

Test data output. Output changes in response to the falling edge of TCK.

This is the output side of the serial registers placed between TDI and TDO.

Notes: The device does not have TRST (TAP reset). The Test-Logic Reset state is entered while TMS is held high for

five rising edges of TCK. The TAP controller state is also reset on SRAM POWER-UP.

TMS

10R

TDI

11R

TDO

1R

TAP DC Operating Characteristics

(Ta = 0 to +70

°

C, V

DD

= 1.8V

±

0.1V)

Unit

V

DD

+ 0.3

V

+0.5

V

+5.0

μ

A

+5.0

μ

A

Parameter

Symbol

V

IH

V

IL

I

LI

I

LO

Min

+1.3

0.3

5.0

5.0

Typ

Max

Notes

Input high voltage

Input low voltage

Input leakage current

Output leakage current

0 V

≤

V

IN

≤

V

DD

0 V

≤

V

IN

≤

V

DD

,

output disabled

I

OLC

= 100

μ

A

I

OLT

= 2 mA

|I

OHC

| = 100

μ

A

|I

OHT

| = 2 mA

Output low voltage

Output high voltage

Notes: 1. All voltages referenced to V

SS

(GND).

2. Power-up: V

IH

≤

V

DDQ

+ 0.3 V and V

DD

≤

+1.7 V and V

DDQ

≤

+1.4 V for t

≤

200 ms.

3. In “EXTEST” mode and “SAMPLE” mode, V

DDQ

is nominally 1.5 V.

4. ZQ: V

IH

= V

DDQ

.

V

OL1

V

OL2

V

OH1

V

OH2

1.6

1.4

0.2

0.4

V

V

V

V

REJ03C0295-0003 Rev.0.03 Jul. 31, 2007

Page 17 of 24

相关PDF资料 |

PDF描述 |

|---|---|

| R1Q3A3618ABG-40R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG-50R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG-60R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3636 | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3636ABG-30R | 36-Mbit QDR™II SRAM 4-word Burst |

相关代理商/技术参数 |

参数描述 |

|---|---|

| R1Q3A3618ABG-40R | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG40RB0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3618ABG40RS0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3618ABG40RT0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3618ABG-50R | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR™II SRAM 4-word Burst |

发布紧急采购,3分钟左右您将得到回复。