- 您现在的位置:买卖IC网 > PDF目录98071 > SB80C186XL25 (INTEL CORP) 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 PDF资料下载

参数资料

| 型号: | SB80C186XL25 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| 封装: | SHRINK, QFP-80 |

| 文件页数: | 6/48页 |

| 文件大小: | 762K |

| 代理商: | SB80C186XL25 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

80C186XL80C188XL

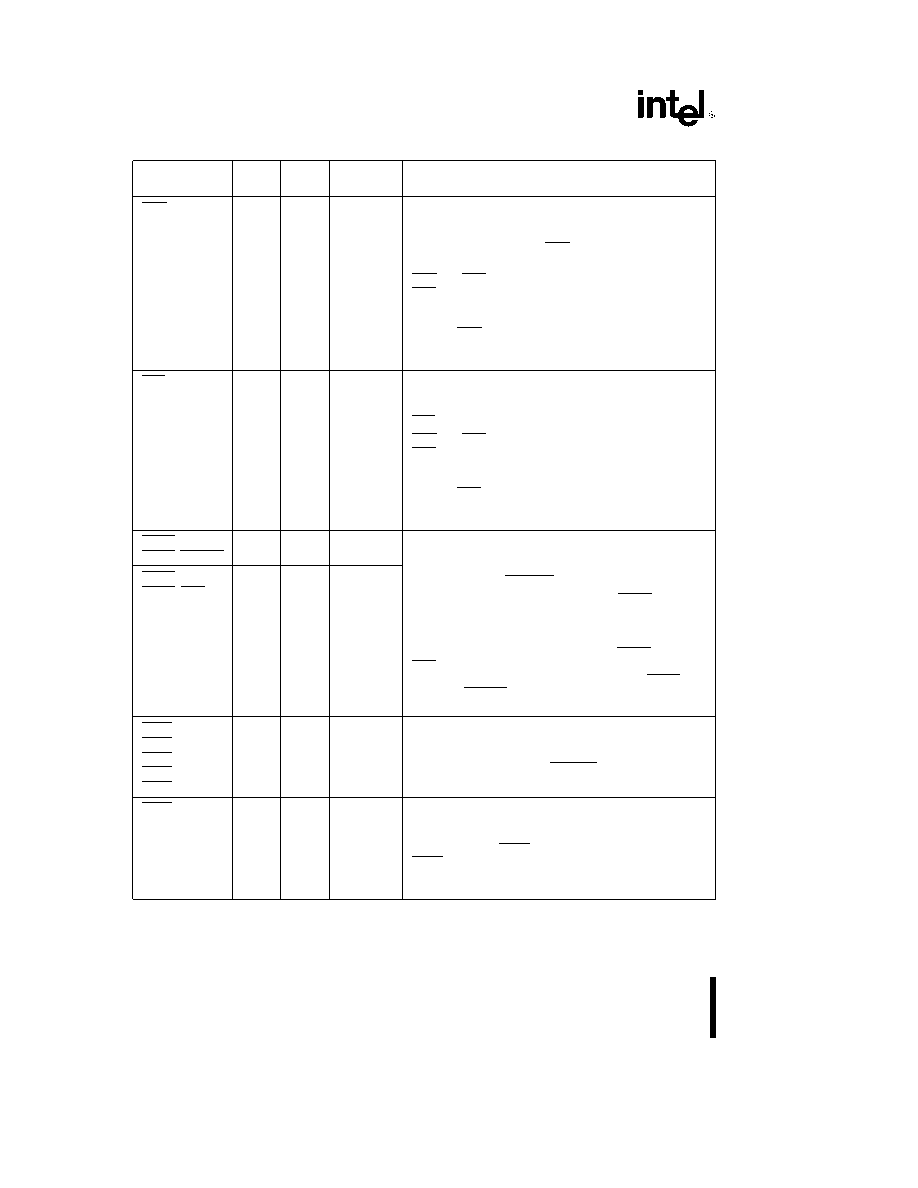

Table 3 Pin Descriptions

(Continued)

Pin

Input

Output

Pin Description

Name

Type

States

UCS

IO

A(L)

H(1)

Upper Memory Chip Select is an active LOW output

whenever a memory reference is made to the defined

R(WH)

upper portion (1K – 256K block) of memory The

address range activating UCS is software

programmable

UCS and LCS are sampled upon the rising edge of

RES If both pins are held low the processor will enter

ONCE Mode In ONCE Mode all pins assume a high

impedance state and remain so until a subsequent

RESET UCS has a weak internal pullup that is active

during RESET to ensure that the processor does not

enter ONCE Mode inadvertently

LCS

IO

A(L)

H(1)

Lower Memory Chip Select is active LOW whenever a

memory reference is made to the defined lower portion

R(WH)

(1K – 256K) of memory The address range activating

LCS is software programmable

UCS and LCS are sampled upon the rising edge of

RES If both pins are held low the processor will enter

ONCE Mode In ONCE Mode all pins assume a high

impedance state and remain so until a subsequent

RESET LCS has a weak internal pullup that is active

only during RESET to ensure that the processor does

not enter ONCE mode inadvertently

MCS0 PEREQ

IO

A(L)

H(1)

Mid-Range Memory Chip Select signals are active LOW

when a memory reference is made to the defined mid-

MCS1 ERROR

R(WH)

range portion of memory (8K – 512K) The address

MCS2

O

H(1)

ranges activating MCS0 – 3 are software programmable

MCS3 NPS

R(1)

On the 80C186XL in Enhanced Mode MCS0 becomes

a PEREQ input (Processor Extension Request) When

connected to the Math Coprocessor this input is used

to signal the 80C186XL when to make numeric data

transfers to and from the coprocessor MCS3 becomes

NPS (Numeric Processor Select) which may only be

activated by communication to the 80C187 MCS1

becomes ERROR in Enhanced Mode and is used to

signal numerics coprocessor errors

PCS0

O

H(1)

Peripheral Chip Select signals 0 – 4 are active LOW

when a reference is made to the defined peripheral

PCS1

R(1)

area (64 Kbyte IO or 1 MByte memory space) The

PCS2

address ranges activating PCS0 – 4 are software

PCS3

programmable

PCS4

PCS5 A1

O

H(1)H(X)

Peripheral Chip Select 5 or Latched A1 may be

programmed to provide a sixth peripheral chip select or

R(1)

to provide an internally latched A1 signal The address

range activating PCS5 is software-programmable

PCS5 A1 does not float during bus HOLD When

programmed to provide latched A1 this pin will retain

the previously latched value during HOLD

NOTE

Pin names in parentheses apply to the 80C188XL

14

相关PDF资料 |

PDF描述 |

|---|---|

| SB80C188XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| S80C188EB-8 | 8-BIT, 8 MHz, MICROPROCESSOR, PQFP80 |

| S80C194 | 16-BIT, 12 MHz, MICROCONTROLLER, PQFP80 |

| S83C198 | MROM, 12 MHz, MICROCONTROLLER, PQFP80 |

| S80C196MC | 16-BIT, 16 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SB80C188 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:CMOS High-Integration 16-Bit Microprocessors |

| SB80C188-12 | 制造商:Advanced Micro Devices 功能描述:MPU 80C88 CISC 16-Bit 12.5MHz 80-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| SB80C188-16 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Advanced Micro Devices 功能描述: 制造商:AMD 功能描述: |

| SB80C188-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| SB80C188-25 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:CMOS High-Integration 16-Bit Microprocessors |

发布紧急采购,3分钟左右您将得到回复。