- 您现在的位置:买卖IC网 > PDF目录98080 > SI5334B-A00121-GMR (SILICON LABORATORIES) PLL BASED CLOCK DRIVER, QCC24 PDF资料下载

参数资料

| 型号: | SI5334B-A00121-GMR |

| 厂商: | SILICON LABORATORIES |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, QCC24 |

| 封装: | 4 X 4 MM, ROHS COMPLIANT, MO-220VGGD-8, QFN-24 |

| 文件页数: | 5/34页 |

| 文件大小: | 233K |

| 代理商: | SI5334B-A00121-GMR |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

Si5334

Preliminary Rev. 0.16

13

2. Functional Description

2.1. Overview

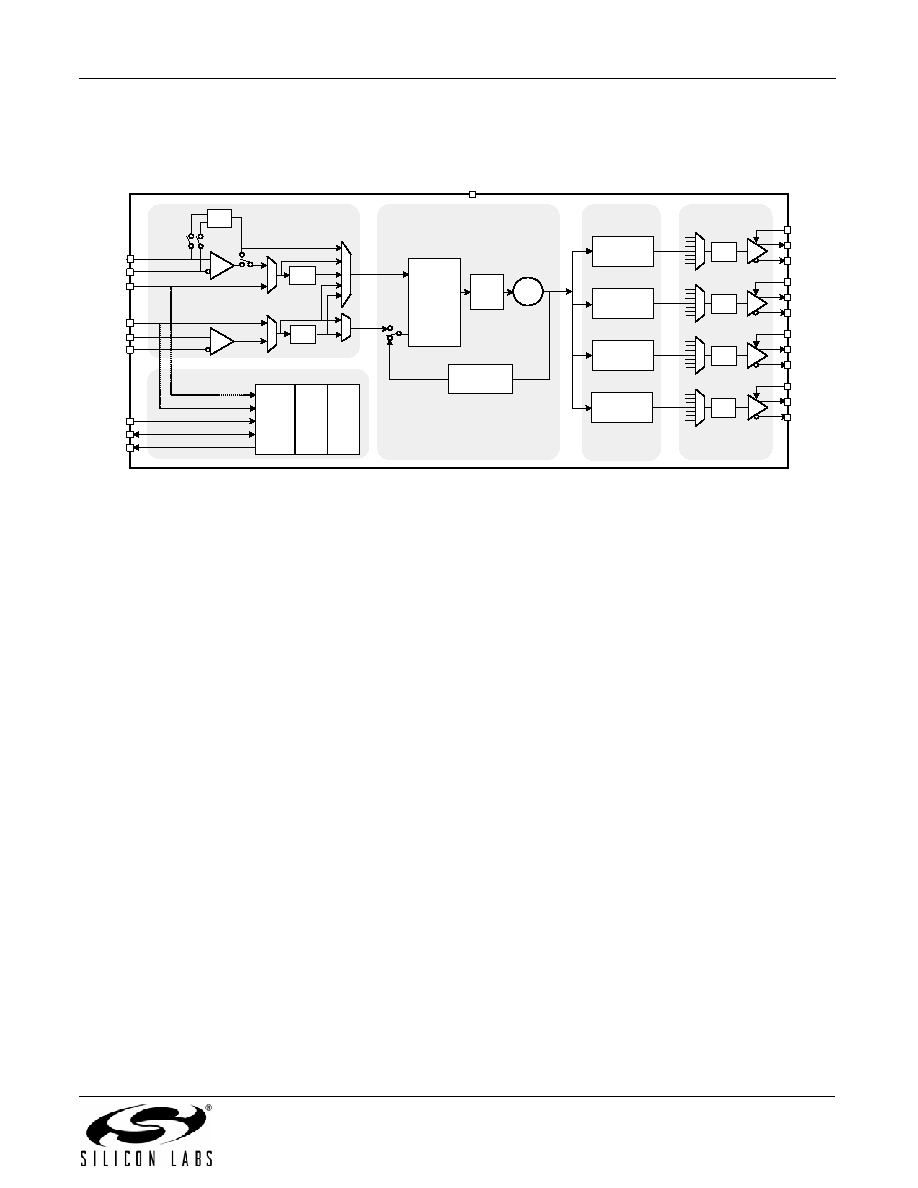

Figure 1. Si5334 Block Diagram

The Si5334 is a high-performance, low-jitter clock

generator capable of synthesizing any frequency on

each of the device's four differential output clocks. The

device accepts an external crystal from 8 to 30 MHz or

an input clock ranging from 5 to 710 MHz. Each output

is

independently

factory-programmable

to

any

frequency up to Fvco/8 (max of 350 MHz) and select

frequencies to 710 MHz.

The Si5334 fractional-N PLL, comprised of a phase

detector, charge pump, loop filter, VCO, and dividers, is

fully integrated on chip to simplify design. Using Silicon

Labs' patented MultiSynth technology, each output clock

is generated with low jitter and zero ppm frequency

error. The device has four MultiSynth output dividers to

provide non-integer frequency synthesis on every

differential output clock.

The Si5334 output driver is highly flexible. The signal

format of each output clock can be user-specified to

support LVPECL, LVDS, HCSL, CMOS, HSTL, or SSTL.

Each output clock has its own supply voltage to allow for

the utmost flexibility in mixed supply operations. The

core of the Si5334 has its own supply voltage that can

be 1.8, 2.5, or 3.3 V.

The Si5334 supports an optional zero delay mode of

operation. In this mode, one of the device output clocks

is fed back to the FDBK/FDBKB clock input pins to

implement the PLL feedback path and nullify the phase

difference between the reference input and the output

clocks.

The Si5334D/E/F has a pin-controlled phase increment/

decrement feature that allows the user to adjust the

phase of each output clock in relation to the other output

clocks. The phase of each differential output clock can

be set to an accuracy of 20 ps over a range of ±45 ns.

This feature is available over the 0.16 to Fvco/8 MHz

frequency range at a maximum rate of phase change of

1.5 MHz.

The

Si5334G/H/J

has

a

pin-controlled

frequency

increment/decrement feature that allows the user to

change frequency in steps as small as 1 ppm of the

initial frequency to as large as possible as long as the

frequency at the output of the MultiSynth stays within

the range of 5 MHz to Fvco/8 MHz. This feature is

available on CLK0A/B only. The frequency step is

glitchless. This feature is useful in applications that

require a variable clock frequency. It can also be used in

frequency margining applications to margin test system

clocks during design/verification/test or manufacturing

test applications.

For EMI reduction, the Si5334K/L/M supports PCI

Express 2.0 compliant spread spectrum on all output

clocks that are 100 MHz.

Phase

Frequency

Detector

Loop

Filter

VCO

CLK0A

÷P2

VDDO1

VDDO2

VDDO3

VDDO0

MultiSynth

÷M0

PDEC/FDEC

PINC/FINC

CLK0B

CLK1A

CLK1B

CLK2A

CLK2B

CLK3A

CLK3B

÷P1

IN3

IN2

IN1

÷R1

MultiSynth

÷M1

MultiSynth

÷M2

MultiSynth

÷M3

IN6

IN4

IN5

Osc

MultiSynth

÷N

Control

NVM

(OTP)

÷R0

÷R2

÷R3

Input

Stage

Synthesis

Stage 1

(PLL)

Synthesis

Stage 2

Output

Stage

Control & Memory

OEB

LOSLOL

VDD

ref

fb

RAM

SSPB

REFCLK1

FDBKSE

XTAL/CLKIN

FDBK

XTAL/CLKINB

FDBKB

相关PDF资料 |

PDF描述 |

|---|---|

| SI5334C-A00115-GM | PLL BASED CLOCK DRIVER, QCC24 |

| SI5334C-A00120-GMR | PLL BASED CLOCK DRIVER, QCC24 |

| SI5334C--A00104-GM | PLL BASED CLOCK DRIVER, QCC24 |

| SI5334C-A00112-GMR | PLL BASED CLOCK DRIVER, QCC24 |

| SI5334C-A00114-GMR | PLL BASED CLOCK DRIVER, QCC24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SI5334B-A00122-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Rail/Tube |

| SI5334B-A00122-GMR | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Tape and Reel |

| SI5334B-A00154-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Rail/Tube |

| SI5334B-A00154-GMR | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Tape and Reel |

| SI5334B-A00156-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。