- 您现在的位置:买卖IC网 > PDF目录299917 > SN65LVDS9637BDG4 (TEXAS INSTRUMENTS INC) DUAL LINE RECEIVER, PDSO8 PDF资料下载

参数资料

| 型号: | SN65LVDS9637BDG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | Buffer和线驱动 |

| 英文描述: | DUAL LINE RECEIVER, PDSO8 |

| 封装: | 1.27 MM PITCH, GREEN, SOIC-8 |

| 文件页数: | 7/22页 |

| 文件大小: | 358K |

| 代理商: | SN65LVDS9637BDG4 |

www.ti.com

_

+

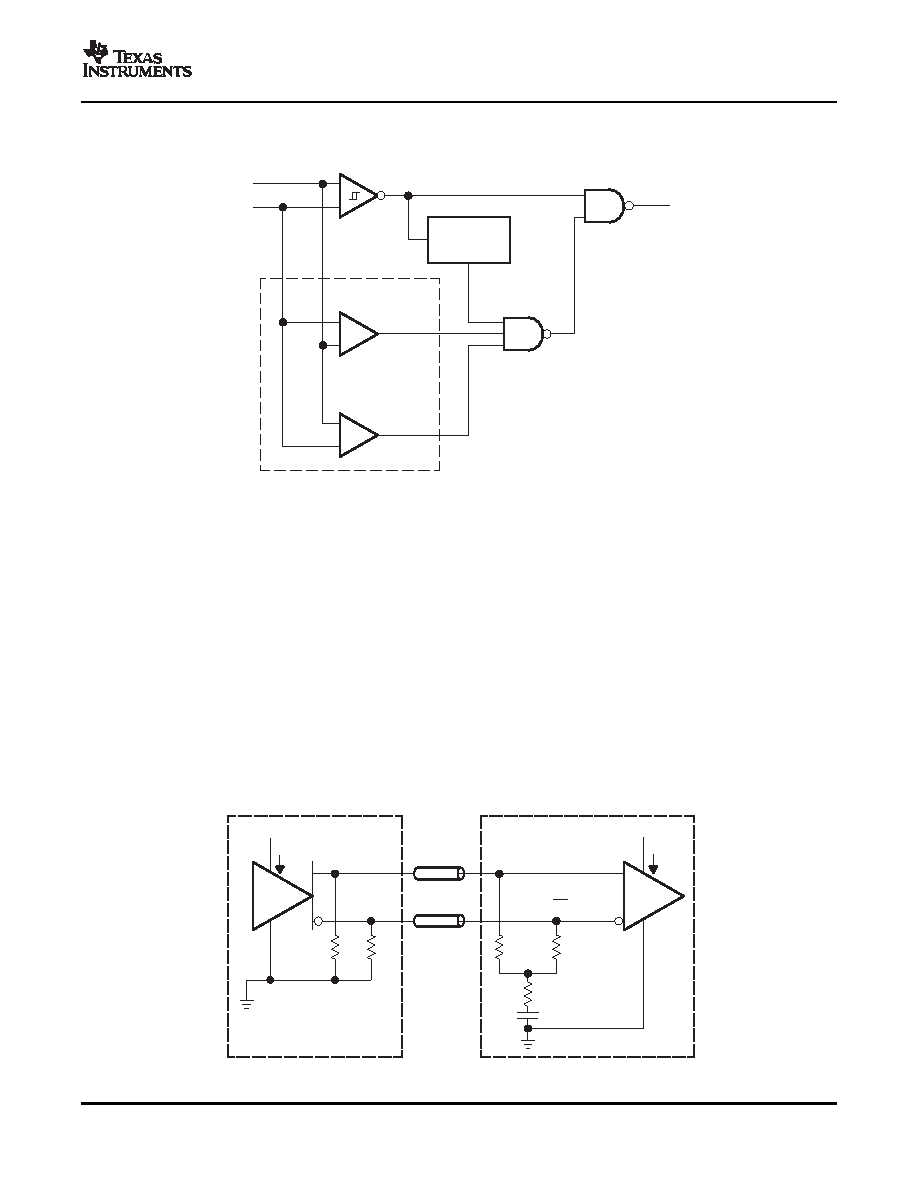

Main Receiver

_

+

_

+

A > B + 80 mV

B > A + 80 mV

Failsafe

Timer

Failsafe

Output

Buffer

Reset

Window Comparator

A

B

R

ECL/PECL-to-LVTTL CONVERSION WITH TI's LVDS RECEIVER

R3

VCC

ICC

5 Meters

of CAT-5

R1

VEE

R2

VCC

ICC

R3 = 240

R1 = 50

R2 = 50

VB

LVDS

LV/PECL

SLLS440B – OCTOBER 2000 – REVISED APRIL 2007

APPLICATION INFORMATION (continued)

Figure 13. Receiver With Terminated Failsafe

The various versions of emitter-coupled logic (i.e., ECL, PECL and LVPECL) are often the physical layer of

choice for system designers. Designers know of the established technology and that it is capable of high-speed

data transmission. In the past, system requirements often forced the selection of ECL. Now technologies like

LVDS provide designers with another alternative. While the total exchange of ECL for LVDS may not be a

design option, designers have been able to take advantage of LVDS by implementing a small resistor divider

network at the input of the LVDS receiver. TI has taken the next step by introducing a wide common-mode

LVDS receiver (no divider network required) which can be connected directly to an ECL driver with only the

termination bias voltage required for ECL termination (VCC– 2 V).

Figure 14 and Figure 15 show the use of an LV/PECL driver driving 5 meters of CAT-5 cable and being received

by TI's wide common-mode receiver and the resulting eye pattern. The values for R3 are required in order to

provide a resistor path to ground for the LV/PECL driver. With no resistor divider, R1 simply needs to match the

characteristic load impedance of 50

. The R2 resistor is a small value and is intended to minimize any possible

common-mode current reflections.

Figure 14. LVPECL or PECL to Remote Wide Common-Mode LVDS Receiver

15

相关PDF资料 |

PDF描述 |

|---|---|

| SN74ALS234DW | 64 X 4 OTHER FIFO, 22 ns, PDSO16 |

| SN74LS374NSRG4 | OCTAL D-TYPE TRANSPARENT LATCHES AND EDGE-TRIGGERED FLIP-FLOPS |

| SN74LV174ADBRG4 | HEX D-TYPE FLIP-FLOPS WITH CLEAR |

| SN74LV174ADG4 | HEX D-TYPE FLIP-FLOPS WITH CLEAR |

| SN74LV174ADGVRE4 | HEX D-TYPE FLIP-FLOPS WITH CLEAR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN65LVDS9637BDR | 功能描述:LVDS 接口集成电路 Dual LVDS RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

| SN65LVDS9637BDRG4 | 功能描述:LVDS 接口集成电路 Dual LVDS Receiver RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

| SN65LVDS9637D | 功能描述:LVDS 接口集成电路 Dual HS Diff RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

| SN65LVDS9637DG4 | 功能描述:LVDS 接口集成电路 DUAL LVDS RECEIVER RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

| SN65LVDS9637DGK | 功能描述:LVDS 接口集成电路 Dual HS Diff RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。