- 您现在的位置:买卖IC网 > PDF目录9884 > SN74ACT7807-25PAG (Texas Instruments)IC SYNC FIFO MEM 2048X9 64-TQFP PDF资料下载

参数资料

| 型号: | SN74ACT7807-25PAG |

| 厂商: | Texas Instruments |

| 文件页数: | 16/20页 |

| 文件大小: | 0K |

| 描述: | IC SYNC FIFO MEM 2048X9 64-TQFP |

| 标准包装: | 160 |

| 系列: | 74ACT |

| 功能: | 同步 |

| 存储容量: | 18.4K(2K x 9) |

| 数据速率: | 67MHz |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-TQFP |

| 供应商设备封装: | 64-TQFP(10x10) |

| 包装: | 托盘 |

| 其它名称: | 296-4465 |

SN74ACT7807

2048

× 9

CLOCKED FIRST-IN, FIRST-OUT MEMORY

SCAS200D – JANUARY 1991 – REVISED APRIL 1998

5

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

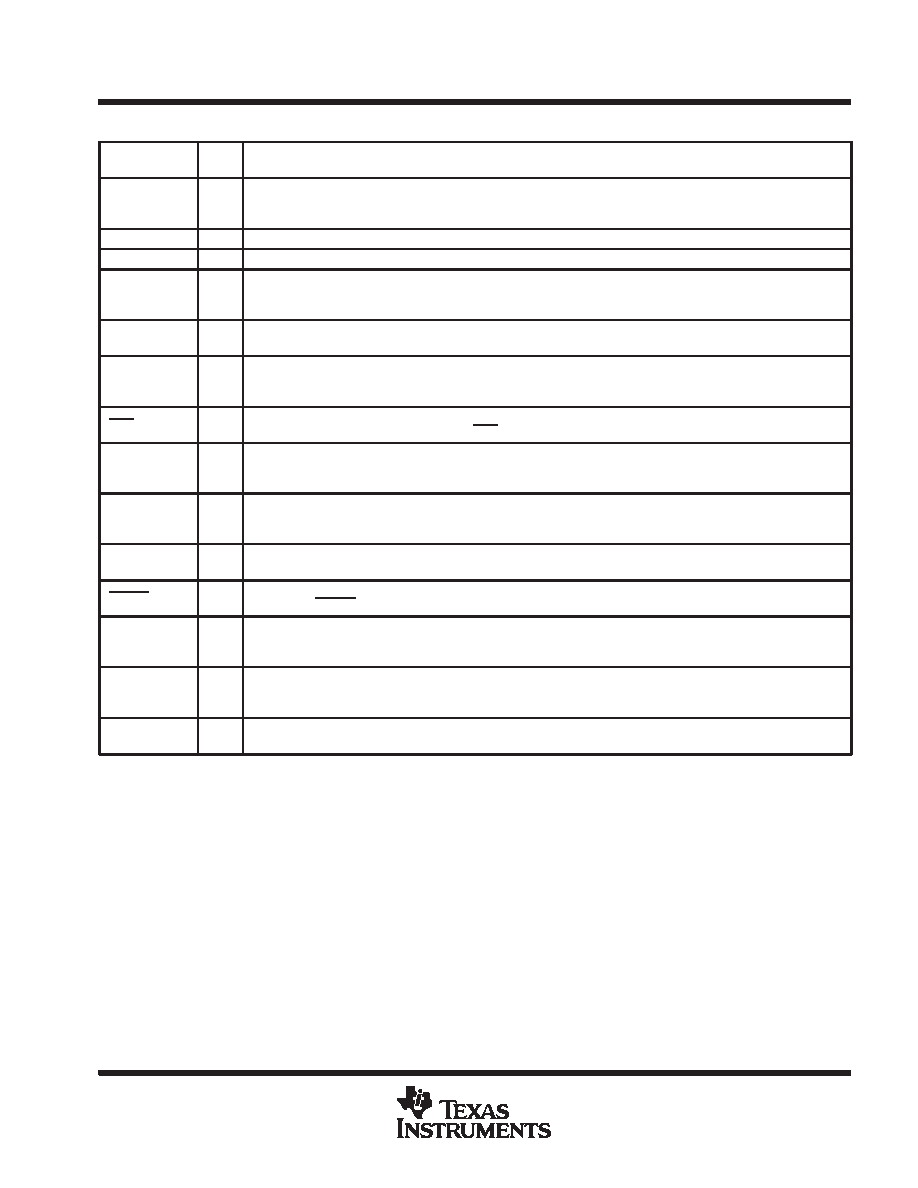

Terminal Functions

TERMINAL

NAME

I/O

DESCRIPTION

AF/AE

O

Almost-full/almost-empty flag. Depth offset values can be programmed for AF/AE or the default value of 256 can

be used for both the almost-empty offset (X) and the almost-full offset (Y). AF/AE is high when memory contains

X or fewer words or (2048 – Y) or more words. AF/AE is high after reset.

D0–D8

I

Nine-bit data input port

HF

O

Half-full flag. HF is high when the FIFO memory contains 1024 or more words. HF is low after reset.

IR

O

Input-ready flag. IR is synchronized to the low-to-high transition of WRTCLK. When IR is low, the FIFO is full and

writes are disabled. IR is low during reset and goes high on the second low-to-high transition of WRTCLK after

reset.

OE

I

Output enable. When OE, RDEN1, RDEN2 and OR are high, data is read from the FIFO on a low-to-high transition

of RDCLK. When OE is low, reads are disabled and the data outputs are in the high-impedance state.

OR

O

Output-ready flag. OR is synchronized to the low-to-high transition of RDCLK. When OR is low, the FIFO is empty

and reads are disabled. Ready data is present on Q0–Q17 when OR is high. OR is low during reset and goes high

on the third low-to-high transition of RDCLK after the first word is loaded to empty memory.

PEN

I

Program enable. After reset and before the first word is written to the FIFO, the binary value on D0–D8 and DP9

is latched as an AF/AE offset value when PEN is low and WRTCLK is high.

Q0–Q8

O

Nine-bit data output port. After the first valid write to empty memory, the first word is output on Q0–Q8 on the third

rising edge of RDCLK. OR also is asserted high at this time to indicate ready data. When OR is low, the last word

read from the FIFO is present on Q0–Q8.

RDCLK

I

Read clock. RDCLK is a continuous clock and can be asynchronous or coincident to WRTCLK. A low-to-high

transition of RDCLK reads data from memory when RDEN1, RDEN2, OE, and OR are high. OR is synchronous

to the low-to-high transition of RDCLK.

RDEN1

RDEN2

I

Read enables. When RDEN1, RDEN2, OE, and OR are high, data is read from the FIFO on the low-to-high

transition of RDCLK.

RESET

I

Reset. To reset the FIFO, four low-to-high transitions of RDCLK and four low-to-high transitions of WRTCLK must

occur while RESET is low. This sets HF, IR, and OR low and AF/AE high.

WRTCLK

I

Write clock. WRTCLK is a continuous clock and can be asynchronous or coincident to RDCLK. A low-to-high

transition of WRTCLK writes data to memory when WRTEN1/DP9, WRTEN2, and IR are high. IR is synchronous

to the low-to-high transition of WRTCLK.

WRTEN1/DP9

I

Write enable/data pin 9. When WRTEN1/DP9, WRTEN2, and IR are high, data is written to the FIFO on a

low-to-high transition of WRTCLK. When programming an AF/AE offset value, WRTEN1/DP9 is used as the

most-significant data bit.

WRTEN2

I

Write enable. When WRTEN1/DP9, WRTEN2, and IR are high, data is written to the FIFO on a low-to-high

transition of WRTCLK.

相关PDF资料 |

PDF描述 |

|---|---|

| V300A15T500BF | CONVERTER MOD DC/DC 15V 500W |

| MS27473E14F15P | CONN PLUG 15POS STRAIGHT W/PINS |

| V300A15T500BL3 | CONVERTER MOD DC/DC 15V 500W |

| MS27656T13A35S | CONN RCPT 22POS WALL MNT W/SCKT |

| MS27656E13A35S | CONN RCPT 22POS WALL MNT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74ACT7807-40FN | 功能描述:先进先出 2048 x 9 synchronous 先进先出 memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74ACT7807-40PAG | 功能描述:先进先出 2048 x 9 synchronous 先进先出 memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74ACT7808-20FN | 功能描述:先进先出 2048 X 9 asynch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74ACT7808-20PAG | 功能描述:先进先出 2048 X 9 asynch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74ACT7808-25FN | 功能描述:先进先出 2048 X 9 asynch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

发布紧急采购,3分钟左右您将得到回复。