- 您现在的位置:买卖IC网 > PDF目录98112 > SN74GTLP1394DGVR (TEXAS INSTRUMENTS INC) GTLP SERIES, 2-BIT TRANSCEIVER, CONFIGURABLE OUTPUT, PDSO16 PDF资料下载

参数资料

| 型号: | SN74GTLP1394DGVR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 总线收发器 |

| 英文描述: | GTLP SERIES, 2-BIT TRANSCEIVER, CONFIGURABLE OUTPUT, PDSO16 |

| 封装: | GREEN, PLASTIC, TVSOP-16 |

| 文件页数: | 1/24页 |

| 文件大小: | 552K |

| 代理商: | SN74GTLP1394DGVR |

www.ti.com

FEATURES

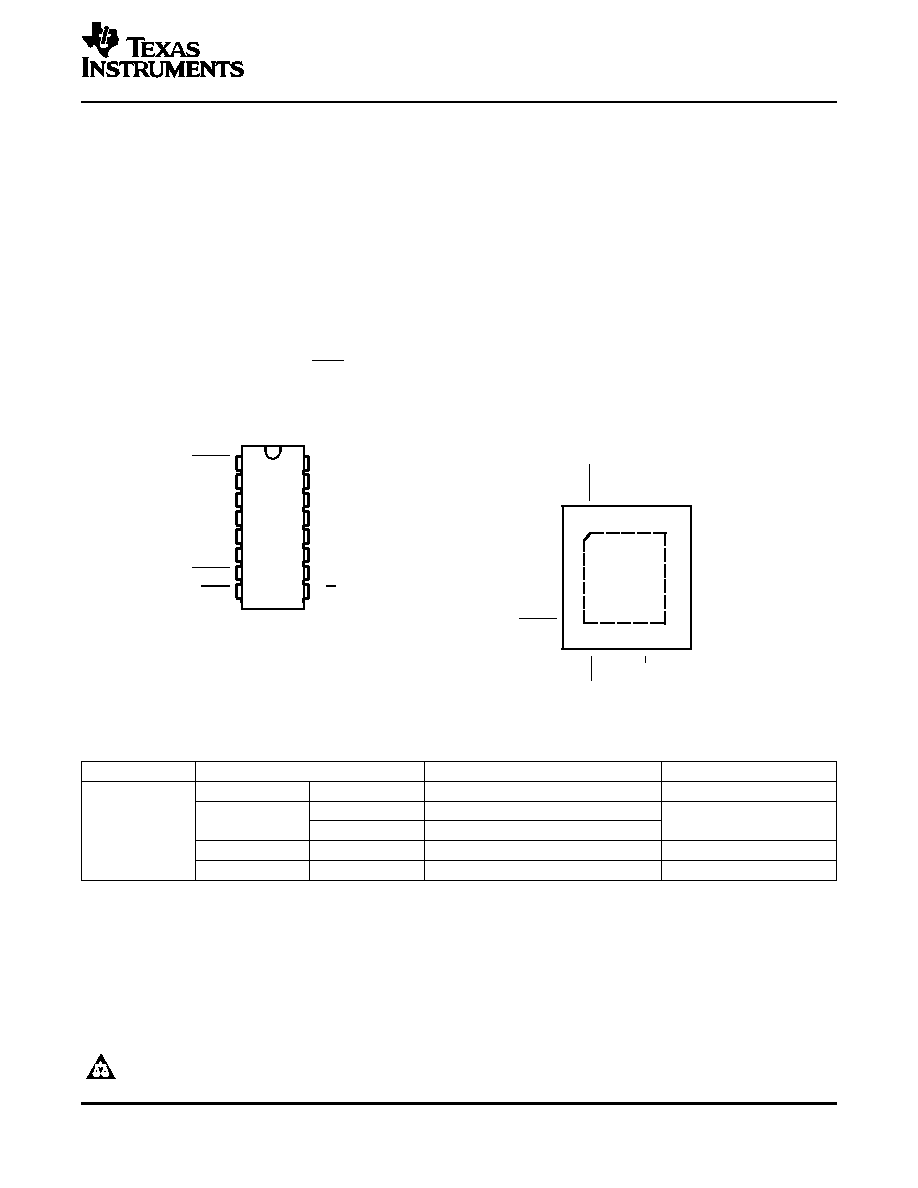

D, DGV, OR PW PACKAGE

(TOP VIEW)

RGY PACKAGE

(TOP VIEW)

1

16

8

9

2

3

4

5

6

7

15

14

13

12

11

10

GND

B1

GND

B2

GND

VREF

Y1

Y2

VCC

A1

A2

OEAB

OEBY

T/C

BIAS

V

ERC

CC

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

OEBY

Y1

Y2

VCC

A1

A2

OEAB

ERC

BIAS VCC

GND

B1

GND

B2

GND

VREF

T/C

DESCRIPTION/ORDERING INFORMATION

SN74GTLP1394

2-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER

WITH SPLIT LVTTL PORT, FEEDBACK PATH, AND SELECTABLE POLARITY

SCES286F – OCTOBER 1999 – REVISED APRIL 2005

Data-Transfer Rate and Signal Integrity in

Distributed Loads

TI-OPC Circuitry Limits Ringing on

Unevenly Loaded Backplanes

Ioff, Power-Up 3-State, and BIAS VCC Support

Live Insertion

OEC Circuitry Improves Signal Integrity and

Reduces Electromagnetic Interference

Polarity Control Selects True or

Complementary Outputs

Bidirectional Interface Between GTLP Signal

Levels and LVTTL Logic Levels

Latch-Up Performance Exceeds 100 mA Per

JESD 78, Class II

Split LVTTL Port Provides a Feedback Path

for Control and Diagnostics Monitoring

ESD Protection Exceeds JESD 22

LVTTL Interfaces Are 5-V Tolerant

– 2000-V Human-Body Model (A114-A)

High-Drive GTLP Outputs (100 mA)

– 200-V Machine Model (A115-A)

LVTTL Outputs (–24 mA/24 mA)

– 1000-V Charged-Device Model (C101)

Variable Edge-Rate Control (ERC) Input

Selects GTLP Rise and Fall Times for Optimal

ORDERING INFORMATION

TA

PACKAGE(1)

ORDERABLE PART NUMBER

TOP-SIDE MARKING

QFN – RGY

Tape and reel

SN74GTLP1394RGYR

GP1394

Tube

SN74GTLP1394D

SOIC – D

GTLP1394

–40°C to 85°C

Tape and reel

SN74GTLP1394DR

TSSOP – PW

Tape and reel

SN74GTLP1394PWR

GP394

TVSOP – DGV

Tape and reel

SN74GTLP1394DGVR

GP394

(1)

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at

www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI-OPC, OEC, TI are trademarks of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Copyright 1999–2005, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

相关PDF资料 |

PDF描述 |

|---|---|

| SN74GTLP2033DGVR | GTLP SERIES, 8-BIT REGISTERED TRANSCEIVER, INVERTED OUTPUT, PDSO48 |

| SN74GTLP2034DGVR | GTLP SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO48 |

| SN74GTLP2034ZQLR | GTLP SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PBGA56 |

| SN74GTLP22034DGVR | GTLP SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO48 |

| SN74GTLP817DGV | GTLP SERIES, 6-BIT DRIVER, INVERTED OUTPUT, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74GTLP1394DR | 功能描述:转换 - 电压电平 2bit Bus RoHS:否 制造商:Micrel 类型:CML/LVDS/LVPECL to LVCMOS/LVTTL 传播延迟时间:1.9 ns 电源电流:14 mA 电源电压-最大:3.6 V 电源电压-最小:3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MLF-8 |

| SN74GTLP1394DRE4 | 功能描述:转换 - 电压电平 2-Bit LVTTL/GTLP Bus Xcvr Adj-Edge-Rate RoHS:否 制造商:Micrel 类型:CML/LVDS/LVPECL to LVCMOS/LVTTL 传播延迟时间:1.9 ns 电源电流:14 mA 电源电压-最大:3.6 V 电源电压-最小:3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MLF-8 |

| SN74GTLP1394DRG4 | 功能描述:转换 - 电压电平 2B LVTTL to GTLP Adj Edg RateBus Xcvr RoHS:否 制造商:Micrel 类型:CML/LVDS/LVPECL to LVCMOS/LVTTL 传播延迟时间:1.9 ns 电源电流:14 mA 电源电压-最大:3.6 V 电源电压-最小:3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MLF-8 |

| SN74GTLP1394PW | 功能描述:转换 - 电压电平 2-Bit LVTTL/GTLP Bus Xcvr Adj-Edge-Rate RoHS:否 制造商:Micrel 类型:CML/LVDS/LVPECL to LVCMOS/LVTTL 传播延迟时间:1.9 ns 电源电流:14 mA 电源电压-最大:3.6 V 电源电压-最小:3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MLF-8 |

| SN74GTLP1394PWE4 | 功能描述:转换 - 电压电平 2-Bit LVTTL/GTLP Bus Xcvr Adj-Edge-Rate RoHS:否 制造商:Micrel 类型:CML/LVDS/LVPECL to LVCMOS/LVTTL 传播延迟时间:1.9 ns 电源电流:14 mA 电源电压-最大:3.6 V 电源电压-最小:3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MLF-8 |

发布紧急采购,3分钟左右您将得到回复。