- 您现在的位置:买卖IC网 > PDF目录374876 > SN8P1602 (SONIX Technology Co., Ltd.) 8-Bit Micro-Controller PDF资料下载

参数资料

| 型号: | SN8P1602 |

| 厂商: | SONIX Technology Co., Ltd. |

| 英文描述: | 8-Bit Micro-Controller |

| 中文描述: | 8位微控制器 |

| 文件页数: | 54/94页 |

| 文件大小: | 540K |

| 代理商: | SN8P1602 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页当前第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页

SN8P1600

8-bit micro-controller

SONiX TECHNOLOGY CO., LTD

Page 54

Revision 1.94

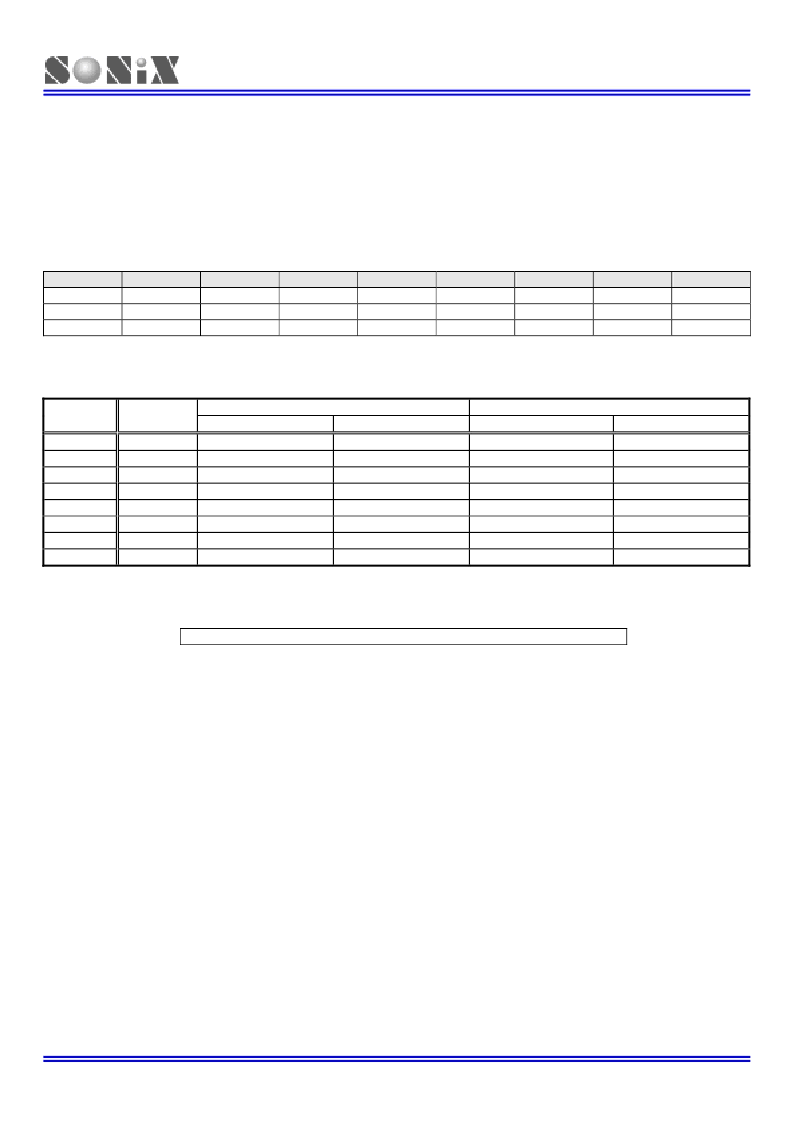

TC0C COUNTING REGISTER

TC0C is an 8-bit counter register for the timer (TC0). TC0C must be reset whenever the TC0ENB is set to “1” to start

the timer. TC0C is incremented each time a clock pulse of the frequency determined by TC0RATE0 ~ TC0RATE2.

When TC0C has incremented to “0FFH”, it counts to “00H” an overflow generated. Under TC0 interrupt service request

(TC0IEN) enable condition, the TC0 interrupt request flag will be set to “1” and the system executes the interrupt

service routine. The TC0C has no auto reload function. After TC0C overflow, the TC0C is continuing counting. Users

need to reset TC0C value to get an accurate time.

0DBH

Bit 7

Bit 6

Bit 5

Bit 4

TC0C

TC0C7

TC0C6

TC0C5

TC0C4

Read/Write

R/W

R/W

R/W

R/W

After reset

0

0

0

0

The basic timer table interval time of TC0.

TC0RATE TC0CLOCK MHigh speed mode (fOne step = max/256

000

fcpu/256

73.2 ms

286us

001

fcpu/128

36.6 ms

143us

010

fcpu/64

18.3 ms

71.5us

011

fcpu/32

9.15 ms

35.8us

100

fcpu/16

4.57 ms

17.9us

101

fcpu/8

2.28 ms

8.94us

110

fcpu/4

1.14 ms

4.47us

111

fcpu/2

0.57 ms

2.23us

The equation of TC0C initial value is as following.

TC0C initial value = 256 - (TC0 interrupt interval time * input clock)

Example: To set 10ms interval time for TC0 interrupt at 3.58MHz high-speed mode. TC0C value (74H) =

256 - (10ms * fcpu/64)

TC0C initial value = 256 - (TC0 interrupt interval time * input clock)

= 256 - (10ms * 3.58 * 10

6

/ 4 / 64)

= 256 - (10

-2

* 3.58 * 10

6

/ 4 / 64)

= 116

= 74H

Bit 3

TC0C3

R/W

0

Bit 2

TC0C2

R/W

0

Bit 1

TC0C1

R/W

0

Bit 0

TC0C0

R/W

0

Low speed mode (fcpu = 32768Hz / 4)

Max overflow interval

8000 ms

4000 ms

2000 ms

1000 ms

500 ms

250 ms

125 ms

62.5 ms

One step = max/256

31.25 ms

15.63 ms

7.8 ms

3.9 ms

1.95 ms

0.98 ms

0.49 ms

0.24 ms

相关PDF资料 |

PDF描述 |

|---|---|

| SN8P1602A | 8-Bit Micro-Controller |

| SN8P1602AK | 8-Bit Micro-Controller |

| SN8P1602AP | 8-Bit Micro-Controller |

| SN8P1602AQ | 8-Bit Micro-Controller |

| SN8P1700A | 8-Bit Micro-Controller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN8P1602A | 制造商:SONIX 制造商全称:SONIX 功能描述:8-Bit Micro-Controller |

| SN8P1602AK | 制造商:SONIX 制造商全称:SONIX 功能描述:8-Bit Micro-Controller |

| SN8P1602AP | 制造商:SONIX 制造商全称:SONIX 功能描述:8-Bit Micro-Controller |

| SN8P1602AQ | 制造商:SONIX 制造商全称:SONIX 功能描述:8-Bit Micro-Controller |

| SN8P1602AS | 制造商:SONIX 制造商全称:SONIX 功能描述:8-Bit Micro-Controller |

发布紧急采购,3分钟左右您将得到回复。