- 您现在的位置:买卖IC网 > PDF目录193594 > SP6342EK1-L-R-A-B/TR 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO6 PDF资料下载

参数资料

| 型号: | SP6342EK1-L-R-A-B/TR |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO6 |

| 封装: | LEAD FREE, MO-193AA, TSOT-6 |

| 文件页数: | 28/32页 |

| 文件大小: | 1342K |

| 代理商: | SP6342EK1-L-R-A-B/TR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页

Date: 4/10/06 Rev J

SP6340 - SP6342 Dual Power Supervisory Circuit

Copyright 2006 Sipex Corporation

5

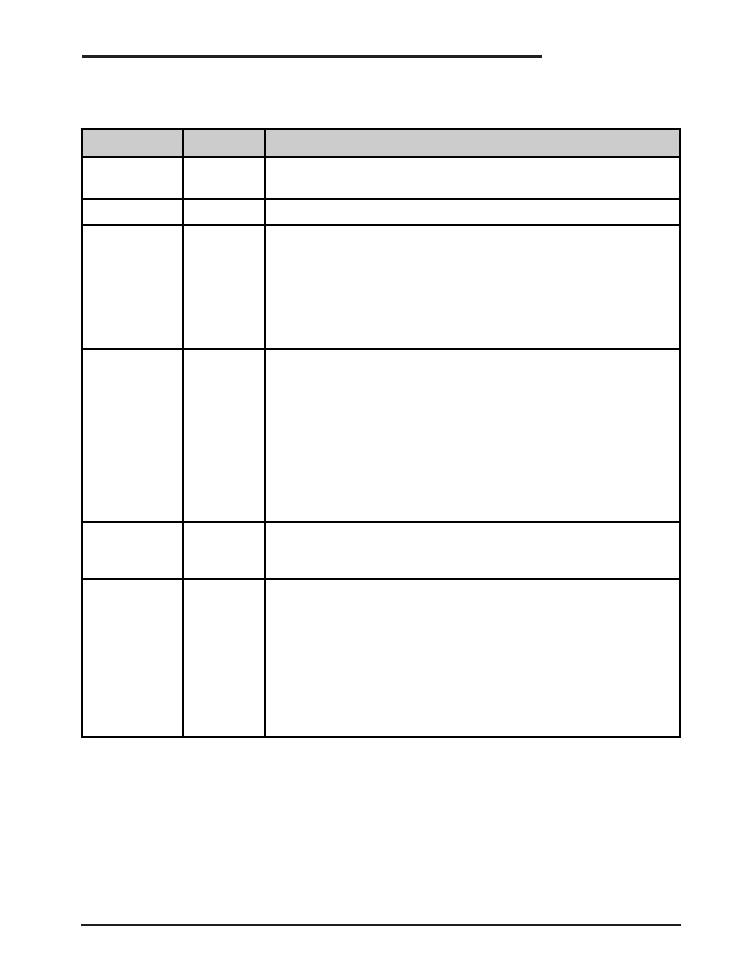

PIN DESCRIPTION

Pin #

Name

Description

1V1

First supply voltage input. Also powers internal circuitry. Trip

threshold voltage internally set.

2V2

Second supply voltage input. Trip threshold voltage internally set.

3

WDI

Watch-Dog Input pin. When no transition is detected at the WDI pin

for the duration of WDI timeout period, reset is asserted. WDOB

remains at “LOW” logic level after watchdog timeout period is

expired and it remains “LOW” until WDI makes a transition.

RST/RSTB output is not affected by the watchdog functionality in the

parts with separate WDOB output. The watchdog timer clears

whenever the reset is asserted or a transition is observed at WDI pin.

4

WDOB

Watch Dog Output. Open-Drain or CMOS, active LOW. If WDI

remains at “HIGH” or “LOW” logic level for longer than the

watchdog timeout period, the internal watchdog timer overflows and

WDOB is asserted. WDOB does not de-assert until the watchdog is

cleared via transition at the WDI pin. Another scenario for WDOB to

assert is when the reset output is asserted due to an under-voltage

V1 or V2 condition. WDO de-asserts without a reset timeout period.

Floating WDI will not disable watchdog timer in devices with

dedicated WDOB output. Open-drain WDOB outputs require an

external pull-up resistor. CMOS outputs are referenced to V1.

5

GND

Common ground reference pin.

6

RSTB

Reset output. Open-Drain or CMOS, active high or low. Reset is

asserted when any of the supply inputs is below its trip threshold. It

stays asserted for 200 ms (typical / default) after the last supply input

traverses its trip threshold. Reset is guaranteed to be in the correct

state for V1>0.9V. RSTB asserts when V1 or V2 drop below their

corresponding reset thresholds. RSTB remains asserted for the

reset timeout period after V1 and V2 exceed their corresponding

reset thresholds. Open-drain outputs require an external pull-up

resistor. CMOS outputs are referenced to V1.

相关PDF资料 |

PDF描述 |

|---|---|

| SP6342EK1-L-S-B-D/TR | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO6 |

| SP6342EK1-L-U-B-C | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO6 |

| SP6342EK1-L-U-C-D | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO6 |

| SP6342EK1-L-U-E-D | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO6 |

| SP6342EK1-L-T-A-C | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SP64/1.2/BLUE | 制造商:Farnell / Pro-Power 功能描述:HEATSHRINK 6.4MM BLUE 1.2M 制造商:pro-power 功能描述:HEATSHRINK, 6.4MM, BLUE, 1.2M 制造商:pro-power 功能描述:HEATSHRINK, 6.4MM, BLUE, 1.2M; I.D. Supplied - Metric:6.4mm; I.D. Supplied - Imperial:0.251"; I.D. Recovered Max - Metric:3.2mm; I.D. Recovered Max - Imperial:0.125"; Shrink Ratio:2:1; Shrink Tubing / Boot Material:PO (Polyolefin); ;RoHS Compliant: Yes |

| SP64/1.2/BLUE | 制造商:Farnell / Pro-Power 功能描述:HEAT SHRINK 6.4MM BLUE 1.2M |

| SP64/1.2/BROWN | 制造商:Farnell / Pro-Power 功能描述:HEAT SHRINK 6.4MM BROWN 1.2M |

| SP64/1.2/BROWN | 制造商:Farnell / Pro-Power 功能描述:HEAT SHRINK 6.4MM BROWN 1.2M |

| SP64/1.2/CLEAR | 制造商:Farnell / Pro-Power 功能描述:HEAT SHRINK 6.4MM CLEAR 1.2M |

发布紧急采购,3分钟左右您将得到回复。