- 您现在的位置:买卖IC网 > PDF目录98141 > SPL505YC264BT (SILICON LABORATORIES) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 PDF资料下载

参数资料

| 型号: | SPL505YC264BT |

| 厂商: | SILICON LABORATORIES |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| 封装: | 6 X 17 MM, LEAD FREE, MO-153, TSSOP-64 |

| 文件页数: | 12/27页 |

| 文件大小: | 314K |

| 代理商: | SPL505YC264BT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

SPL505YC264BT

Rev 1.4 May 21, 2007

Page 2 of 27

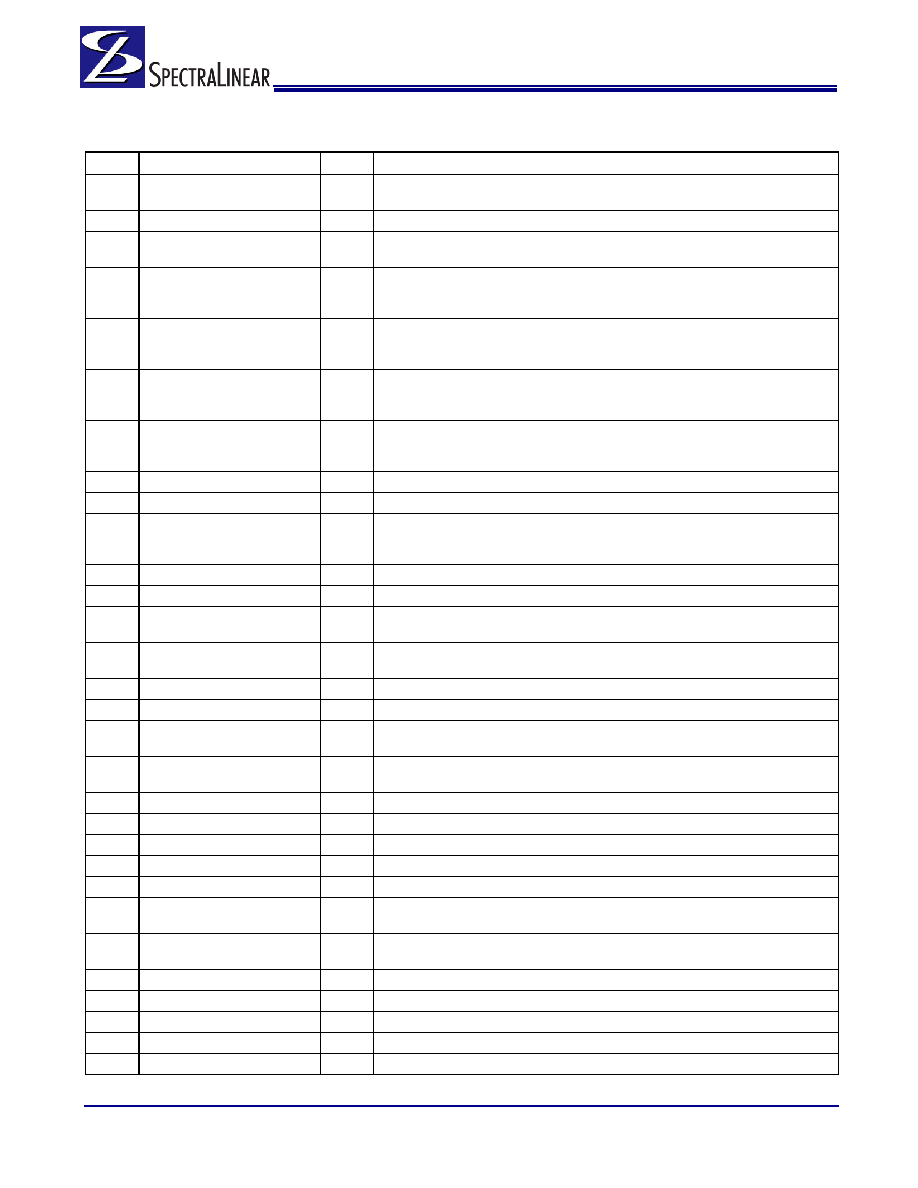

Pin Definitions

Pin No.

Name

Type

Description

1

PCI_0/OE#_0/2_A

I/O, SE 33 MHz clock/3.3V OE# Input mappable via I2C to control either SRC 0 or

SRC 2. Default PCI0

2

VDD_PCI

PWR

3.3V Power supply for PCI PLL.

3

PCI_1/OE#_1/4_A

I/O, SE 33 MHz clock/3.3V OE# Input mappable via I2C to control either SRC 1 or

SRC 4. Default PCI1.

4

PCI_2/TME

I/O, SE 3.3V tolerance input for overclocking enable pin 33 MHz clock.

Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifica-

tions.

5

PCI_3/CFG0

I/O, SE,

PD

3.3V tolerant input for CPU frequency selection/33 MHz clock.

Refer to DC Electrical Specifications table for Vil_PCI3/CFG0 and

Vih_PCI3/CFG0 specifications.

6

PCI_4/SRC5_SEL

I/O, SE 3.3V tolerant input to enable SRC5/33 MHz clock output.

(sampled on the CK_PWRGD assertion)

1 = SRC5, 0 = CPU_STOP#

7

PCIF_0/ITP_EN

I/O, SE 3.3V LVTTL input to enable SRC8 or CPU2_ITP/33 MHz clock output.

(sampled on the CK_PWRGD assertion)

1 = CPU2_ITP, 0 = SRC8

8

VSS_PCI

GND

Ground for outputs.

9

VDD_48

PWR

3.3V Power supply for outputs and PLL.

10

USB_48/FSA

I/O

3.3V tolerant input for CPU frequency selection/fixed 48 MHz clock output.

Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifica-

tions.

11

VSS_48

GND

Ground for outputs.

12

VDD_IO

PWR

0.7V Power supply for outputs.

13

SRC0/DOT96T

O, DIF 100 MHz Differential serial reference clocks/Fixed 96 MHz clock output.

Selected via I2C default is SRC0.

14

SRC0#/DOT96#

O, DIF 100 MHz Differential serial reference clocks/Fixed 96 MHz clock output.

Selected via I2C default is SRC0.

15

VSS_IO

GND

Ground for PLL2.

16

VDD_PLL3

PWR

3.3V Power supply for PLL3

17

SRC1/LCD_100/SE1

O, DIF,

SE

100 MHz Differential serial reference clocks/100 MHz LCD video clock/SE1

clocks. Default SRC1

18

SRC1#/LCD_100#/SE2

O, DIF,

SE

100 MHz Differential serial reference clocks/100 MHz LCD video clock/SE2

clocks. Default SRC1

19

VSS_PLL3

GND

Ground for PLL3.

20

VDD_PLL3_IO

PWR

0.7V Power supply for PLL3 outputs.

21

SRC2/SATA

O, DIF 100 MHz Differential serial reference clocks.

22

SRC2#/SATA#

O, DIF 100 MHz Differential serial reference clocks.

23

VSS_SRC

GND

Ground for outputs.

24

SRC3/OE#_0/2_B

I/O,

Dif

100-MHz Differential serial reference clocks / 3.3V OE#_0/2_B, input,

mappable via I2C to control either SRC 0 or SRC 2. Default SRC3

25

SRC3#OE#_1/4_B

I/O,

Dif

100-MHz Differential serial reference clocks / 3.3V OE#_1/4_B input,

mappable via I2C to control either SRC 1 or SRC 4. Default SRC3

26

VDD_SRC_IO

PWR

0.7V power supply for SRC outputs.

27

SRC4

O, DIF 100 MHz Differential serial reference clocks.

28

SRC4#

O, DIF 100 MHz Differential serial reference clocks.

29

VSS_SRC

GND

Ground for outputs.

30

SRC9

O, DIF 100 MHz Differential serial reference clocks.

相关PDF资料 |

PDF描述 |

|---|---|

| SPW08F0D | SINGLE COLOR LED, PURE WHITE, 3.5 mm |

| SSC-SFT825N-S | TRIPLE COLOR LED, RED/GREEN/BLUE, 2.4 mm |

| SSI32C452-CP | 20 Mbps, ST506; ST412; ST412HP; SA100 COMPATIBLE, FIXED DISK CONTROLLER, PDIP40 |

| SSO-CLD-JK2-1-I2 | SINGLE COLOR LED, ORANGE, 1.6 mm |

| SSS-CLD-HJ2-1-I2 | SINGLE COLOR LED, SUPER RED, 1.6 mm |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SPL505YC264BTT | 功能描述:时钟发生器及支持产品 CK505 v0.85 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SPL5100PT | 制造商:CHENMKO 制造商全称:Chenmko Enterprise Co. Ltd. 功能描述:SCHOTTKY BARRIER RECTIFIER |

| SPL520LLPT | 制造商:CHENMKO 制造商全称:Chenmko Enterprise Co. Ltd. 功能描述:SCHOTTKY BARRIER RECTIFIER |

| SPL53-1024 | 制造商:Power-One 功能描述: |

| SPL53-4000 | 制造商:Power-One 功能描述: |

发布紧急采购,3分钟左右您将得到回复。