- 您现在的位置:买卖IC网 > PDF目录297426 > SPT9712BIN (FAIRCHILD SEMICONDUCTOR CORP) PARALLEL, WORD INPUT LOADING, 0.013 us SETTLING TIME, 12-BIT DAC, PDIP28 PDF资料下载

参数资料

| 型号: | SPT9712BIN |

| 厂商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分类: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 0.013 us SETTLING TIME, 12-BIT DAC, PDIP28 |

| 封装: | PLASTIC, DIP-28 |

| 文件页数: | 2/8页 |

| 文件大小: | 49K |

| 代理商: | SPT9712BIN |

SPT

2

3/3/98

SPT9712

ABSOLUTE MAXIMUM RATING (Beyond which damage may occur)1

Supply Voltages

Negative Supply Voltage (VEE) ................................ -7 V

A/D Ground Voltage Differential .............................. 0.5 V

Input Voltages

Digital Input Voltage (D1-D12, Latch Enable) .................

....................................................................... 0 V to VEE

Control Amp Input Voltage Range ................. 0 V to -4 V

Reference Input Voltage Range (VREF) ......... 0 V to VEE

Output Currents

Internal Reference Output Current ....................... 500

A

Control Amplifier Output Current ........................

±2.5 mA

Temperature

Operating Temperature .............................. -40 to +85

°C

Junction Temperature ......................................... +150

°C

Lead, Soldering (10 seconds) ............................. +300

°C

Storage ..................................................... -65 to +150

°C

Note: 1. Operation at any Absolute Maximum Ratings is not implied. See Electrical Specifications for proper nominal applied

conditions in typical applications.

1Gain is measured as a ratio of the full-scale current to ISET. The ratio is nominally 128.

2Measured as voltage at mid-scale transition to

±0.024%; RL=50 .

3Measured from the rising edge of Latch Enable to where the output signal has left a 1 LSB error band.

4Glitch is measured as the largest single transient.

5Calculated using IFS =128 x

Control Amp In

RSET

6SFDR is defined as the difference in signal energy between the fundamental and worst case spurious frequencies in the output

spectrum window, which is centered at the fundamental frequency and covers the indicated span.

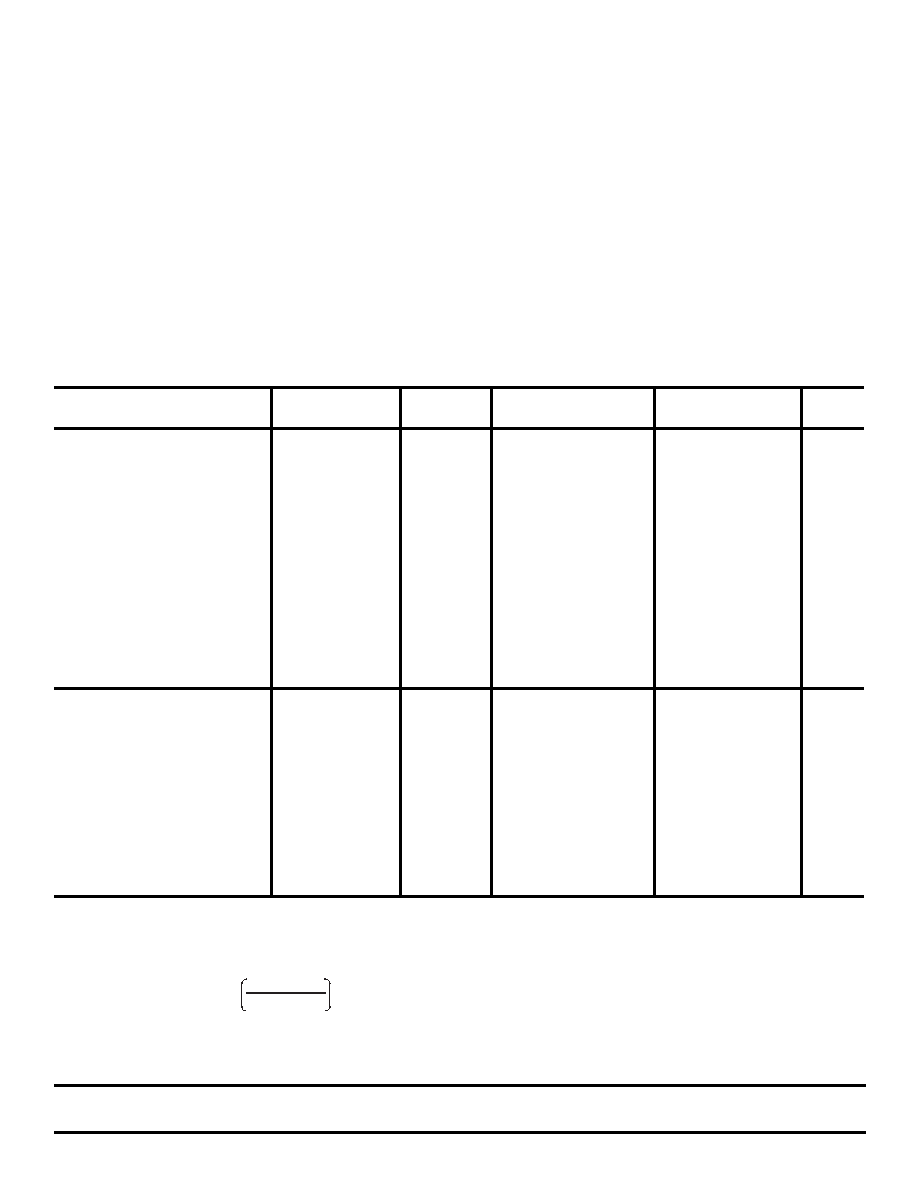

DC Performance

Resolution

12

Bits

Differential Linearity

I

±0.5 ±0.75

±1.0 ±1.25 LSB

Differential Linearity

Max at Full Temp.

VI

±1.5

±2.0 LSB

Integral Linearity

Best Fit

I

±0.75

±1.0

±1.5 LSB

Integral Linearity

Max at Full Temp.

VI

±1.75

±2.0 LSB

Output Capacitance

+25

°C

V

10

pF

Gain Error1

+25

°C

I

1.0

5.0

1.0

5.0

% FS

Full Temp.

VI

8.0

% FS

Gain Error Tempco

Full Temp.

V

150

PPM/

°C

Zero-Scale Offset Error

+25

°C

I

0.5

2.5

0.5

2.5

A

Full Temp.

VI

5.0

A

Offset Drift Coefficient

Full Temp.

V

0.01

A/°C

Output Compliance Voltage

+25

°C

IV

-1.2

+2.0

-1.2

+2.0

V

Equivalent Output Resistance

+25

°C

IV

0.8

1.0

1.2

0.8

1.0

1.2

k

Dynamic Performance

Conversion Rate

+25

°C

IV

100

MWPS

Settling Time tST2

+25

°C

V

13

ns

Output Propagation Delay tD 3

+25

°CV

1

ns

Glitch Energy4

+25

°C

V

15

pV-s

Full Scale Output Current5

+25

°C

V

20.48

mA

Spurious-Free Dynamic Range6

+25

°C

1.23 MHz; 10 MWPS

2 MHz Span

V

70

dBc

5.055 MHz; 20 MWPS

2 MHz Span

V

68

dBc

10.1 MHz; 50 MWPS

2 MHz Span

V

68

dBc

16 MHz; 40 MWPS

10 MHz Span

V

68

dBc

Rise Time / Fall Time

RL = 50

V2

2

ns

ELECTRICAL SPECIFICATIONS

TA = TMIN - TMAX, VEE = -5.2 V, RSET = 7.5 k, Control Amp In = Ref Out, VOUT = 0 V, unless otherwise specified.

TEST

SPT9712A

SPT9712B

PARAMETERS

CONDITIONS

LEVEL

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

相关PDF资料 |

PDF描述 |

|---|---|

| SPX-2000 | INDUSTRY LEADERS DEPEND ON US ...FOR SOLUTIONS |

| SPX1083AU-L | 1.2 V-ADJUSTABLE POSITIVE LDO REGULATOR, 1.2 V DROPOUT, PSFM3 |

| SPX1083AU-L-3.3 | 3.3 V FIXED POSITIVE LDO REGULATOR, 1.2 V DROPOUT, PSFM3 |

| SPX1083AU-L-5.0 | 5 V FIXED POSITIVE LDO REGULATOR, 1.2 V DROPOUT, PSFM3 |

| SPX1083U-L-3.3 | 3.3 V FIXED POSITIVE LDO REGULATOR, 1.2 V DROPOUT, PSFM3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SPT9712BIP | 制造商:CADEKA 制造商全称:CADEKA 功能描述:12-BIT, 100 MWPS ECL D/A CONVERTER |

| SPT9713 | 制造商:CADEKA 制造商全称:CADEKA 功能描述:12-BIT, 100 MWPS TTL D/A CONVERTER |

| SPT9713AIP | 制造商:CADEKA 制造商全称:CADEKA 功能描述:12-BIT, 100 MWPS TTL D/A CONVERTER |

| SPT9713BIP | 功能描述:数模转换器- DAC D/A CONVERTER 12-BIT 100MWPS 640mW RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| SPTA 1.5/ 4-5.08 | 制造商:Vishay BCcomponents 功能描述: |

发布紧急采购,3分钟左右您将得到回复。