- 您现在的位置:买卖IC网 > PDF目录365737 > SST89E516RD2 (Silicon Storage Technology, Inc.) FlashFlex51 MCU PDF资料下载

参数资料

| 型号: | SST89E516RD2 |

| 厂商: | Silicon Storage Technology, Inc. |

| 英文描述: | FlashFlex51 MCU |

| 中文描述: | FlashFlex51单片机 |

| 文件页数: | 47/91页 |

| 文件大小: | 984K |

| 代理商: | SST89E516RD2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页当前第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页

Preliminary Specifications

FlashFlex51 MCU

SST89E52RD2 / SST89E54RD2 / SST89E58RD2 / SST89E516RD2

SST89V52RD2 / SST89V54RD2 / SST89V58RD2 / SST89V516RD2

47

2004 Silicon Storage Technology, Inc.

S71255-00-000

3/04

6.1.2 Automatic Address Recognition

Automatic Address Recognition helps to reduce the MCU

time and power required to talk to multiple serial devices.

Each device is hooked together sharing the same serial

link with its own address. In this configuration, a device is

only interrupted when it receives its own address, thus

eliminating the software overhead to compare addresses.

This same feature helps to save power because it can be

used in conjunction with idle mode to reduce the system’s

overall power consumption. Since there may be multiple

slaves hooked up serial to one master, only one slave

would have to be interrupted from idle mode to respond to

the master’s transmission. Automatic Address Recognition

(AAR) allows the other slaves to remain in idle mode while

only one is interrupted. By limiting the number of interrup-

tions, the total current draw on the system is reduced.

There are two ways to communicate with slaves: a group of

them at once, or all of them at once. To communicate with a

group of slaves, the master sends out an address called

the given address. To communicate with all the slaves, the

master sends out an address called the “broadcast”

address.

AAR can be configured as mode 2 or 3 (9-bit modes) and

setting the SM2 bit in SCON. Each slave has its own SM2

bit set waiting for an address byte (9th bit = 1). The Receive

Interrupt (RI) flag will only be set when the received byte

matches either the given address or the broadcast

address. Next, the slave then clears its SM2 bit to enable

reception of the data bytes (9th bit = 0) from the master.

When the 9th bit = 1, the master is sending an address.

When the 9th bit = 0, the master is sending actual data.

If mode 1 is used, the stop bit takes the place of the 9th bit.

Bit RI is set only when the received command frame

address matches the device’s address and is terminated

by a valid stop bit. Note that mode 0 cannot be used. Set-

ting SM2 bit in the SCON register in mode 0 will have no

effect.

Each slave’s individual address is specified by SFR

SADDR. SFR SADEN is a mask byte that defines “don’t

care” bits to form the given address when combined with

SADDR. See the example below:

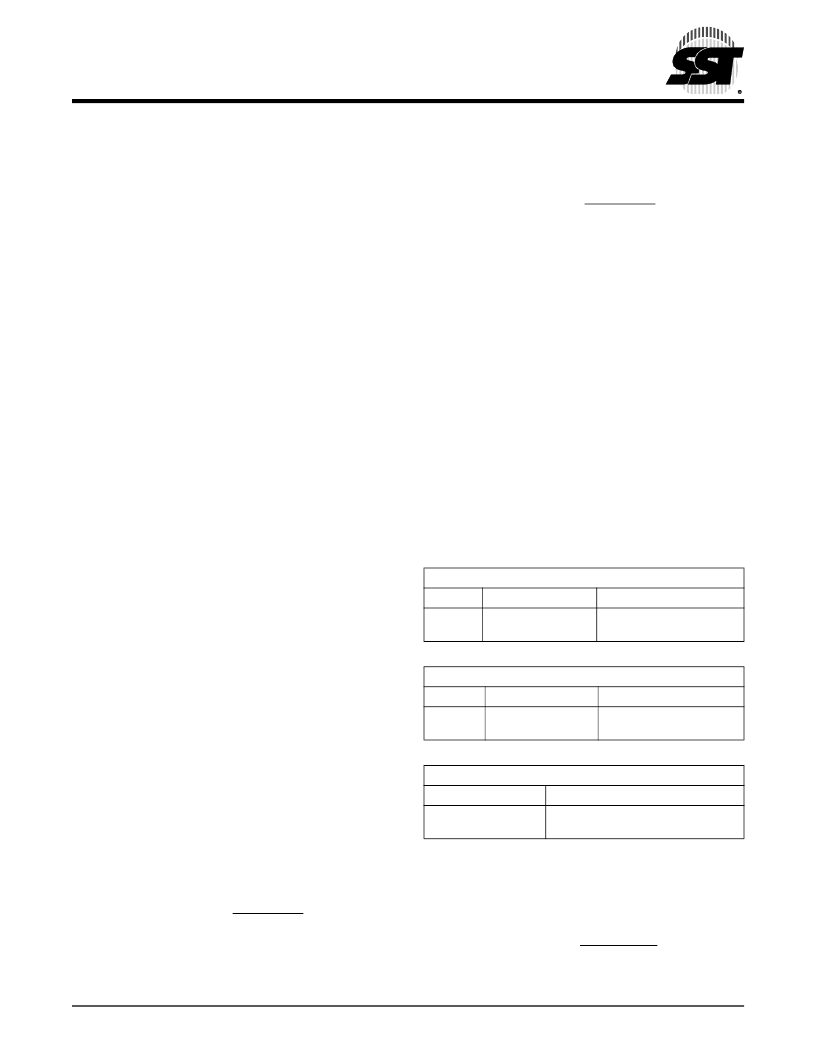

6.1.2.1 Using the Given Address to Select Slaves

Any bits masked off by a 0 from SADEN become a “don’t

care” bit for the given address. Any bit masked off by a 1,

becomes ANDED with SADDR. The “don’t cares” provide

flexibility in the user-defined addresses to address more

slaves when using the given address.

Shown in the example above, Slave 1 has been given an

address of 1111 0001 (SADDR). The SADEN byte has

been used to mask off bits to a given address to allow more

combinations of selecting Slave 1 and Slave 2. In this case

for the given addresses, the last bit (LSB) of Slave 1 is a

“don’t care” and the last bit of Slave 2 is a 1. To communi-

cate with Slave 1 and Slave 2, the master would need to

send an address with the last bit equal to 1 (e.g. 1111

0001) since Slave 1’s last bit is a don’t care and Slave 2’s

last bit has to be a 1. To communicate with Slave 1 alone,

the master would send an address with the last bit equal to

0 (e.g. 1111 0000), since Slave 2’s last bit is a 1. See the

table below for other possible combinations.

If the user added a third slave such as the example below:

Slave 1

SADDR

SADEN

GIVEN

=

=

=

1111 0001

1111 1010

1111 0X0X

Slave 2

SADDR

SADEN

GIVEN

=

=

=

1111 0011

1111 1001

1111 0XX1

Select Slave 1 Only

Given Address

1111 0X0X

Slave 1

Possible Addresses

1111 0000

1111 0100

Select Slave 2 Only

Given Address

1111 0XX1

Slave 2

Possible Addresses

1111 0111

1111 0011

Select Slaves 1 & 2

Slaves 1 & 2

Possible Addresses

1111 0001

1111 0101

Slave 3

SADDR =

SADEN =

GIVEN

1111

1111

1111 X0X1

1001

0101

=

相关PDF资料 |

PDF描述 |

|---|---|

| SST89E516RD2-33-C-NI | FlashFlex51 MCU |

| SST89E516RD2-33-C-NJ | FlashFlex51 MCU |

| SST89E516RD2-33-C-PI | FlashFlex51 MCU |

| SST89E516RD2-33-C-PJ | FlashFlex51 MCU |

| SST89V58RD2-40-I-PJ | FlashFlex51 MCU |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SST89E516RD2_07 | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex MCU |

| SST89E516RD2_13 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:FlashFlex MCU |

| SST89E516RD2-33-C-NI | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E516RD2-33-C-NJ | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E516RD2-33-C-PI | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

发布紧急采购,3分钟左右您将得到回复。