- 您现在的位置:买卖IC网 > PDF目录195454 > SSTV16857MTDX (FAIRCHILD SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | SSTV16857MTDX |

| 厂商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分类: | 锁存器 |

| 中文描述: | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO48 |

| 封装: | 6.10 MM, MO-153, TSSOP-48 |

| 文件页数: | 5/7页 |

| 文件大小: | 85K |

| 代理商: | SSTV16857MTDX |

5

www.fairchildsemi.com

SSTV168

57

SSTVN16857

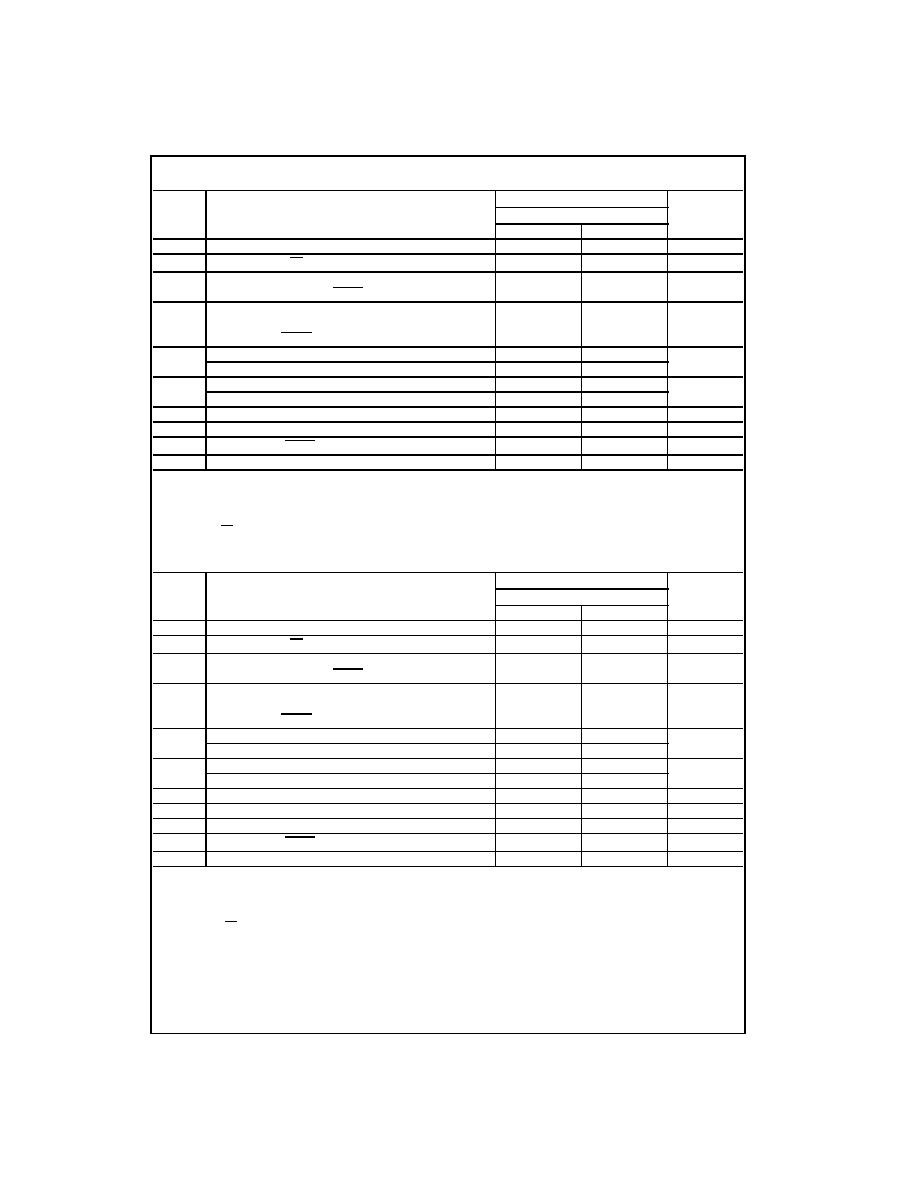

AC Electrical Characteristics (SSTV16857) (Note 4)

Note 4: Refer to Figure 1 through Figure 7.

Note 5: This parameter is not production tested.

Note 6: For data signal input slew rate

t 1 V/ns.

Note 7: For data signal input slew rate

t 0.5 V/ns and 1 V/ns.

Note 8: For CK, CK signals input slew rates are

t 1 V/ns.

AC Electrical Characteristics (SSTVN16857) (Note 9)

Note 9: Refer to Figure 1 through Figure 7.

Note 10: This parameter is not production tested.

Note 11: For data signal input slew rate

t 1 V/ns.

Note 12: For data signal input slew rate

t 0.5 V/ns and 1 V/ns.

Note 13: For CK, CK signals input slew rates are

t 1 V/ns.

Note 14: Simultaneous Switching is guaranteed by characterization.

Symbol

Parameter

TA 0qC to 70qC, CL 30 pF, RL 50:

Units

VDD 2.5V r 0.2V; VDDQ 2.5V r 0.2V

Min

Max

fMAX

Maximum Clock Frequency

200

MHz

tW

Pulse Duration, CK, CK HIGH or LOW (Figure 2)

2.5

ns

tACT

Differential Inputs Activation Time,

22

ns

(Note 5)

data inputs must be LOW after RESET HIGH (Figure 3)

tINACT

Differential Inputs De-activation Time,

22

ns

(Note 5)

data and clock inputs must be held at valid levels

(not floating) after RESET LOW

tS

Setup Time, Fast Slew Rate (Note 6)(Note 7) (Figure 5)

0.65

ns

Setup Time, Slow Slew Rate (Note 7)(Note 8) (Figure 5)

0.9

tH

Hold Time, Fast Slew Rate (Note 6)(Note 8) (Figure 5)

0.75

ns

Hold Time, Slow Slew Rate (Note 7)(Note 8) (Figure 5)

0.9

tREM

Reset Removal Time (Figure 7)

10

ns

tPHL, tPLH

Propagation Delay CLK, CLK to Qn (Figure 4)

1.1

2.8

ns

tPHL

Propagation Delay RESET to Qn (Figure 6)

5.0

ns

tSK(Pn-Pn)

Output to Output Skew

200

ps

Symbol

Parameter

TA 0qC to 70qC, CL 30 pF, RL 50:

Units

VDD 2.5V r 0.2V; VDDQ 2.5V r 0.2V

Min

Max

fMAX

Maximum Clock Frequency

220

MHz

tW

Pulse Duration, CK, CK HIGH or LOW (Figure 2)

2.5

ns

tACT

Differential Inputs Activation Time,

22

ns

(Note 5)

data inputs must be LOW after RESET HIGH (Figure 3)

tINACT

Differential Inputs De-activation Time,

22

ns

(Note 5)

Data and Clock Inputs must be held at valid levels

(not floating) after RESET LOW

tS

Setup Time, Fast Slew Rate (Note 9)(Note 12) (Figure 5)

0.65

ns

Setup Time, Slow Slew Rate (Note 12)(Note 13) (Figure 5)

0.75

tH

Hold Time, Fast Slew Rate (Note 11)(Note 13) (Figure 5)

0.75

ns

Hold Time, Slow Slew Rate (Note 12)(Note 13) (Figure 5)

0.9

tREM

Reset Removal Time (Figure 7)

10

ns

tPHL, tPLH

Propagation Delay CLK, CLK to Qn (Figure 4)

1.1

2.4

ns

tPSS

Propagation Delay Simultaneous Switching CLK, CLK to Qn (Note 14)

2.7

ns

tPHL

Propagation Delay RESET to Qn (Figure 6)

5.0

ns

tSK(Pn-Pn)

Output to Output Skew

200

ps

相关PDF资料 |

PDF描述 |

|---|---|

| SSTV16857MTDX_NL | |

| SSTV16857MTD_NL | |

| SSW-1-05-22-SM-S-VS | 5 CONTACT(S), FEMALE, STRAIGHT TWO PART BOARD CONNECTOR, SURFACE MOUNT |

| SSW-1-05-22-STL-T-VS | 15 CONTACT(S), FEMALE, STRAIGHT TWO PART BOARD CONNECTOR, SURFACE MOUNT |

| SSW-1-06-22-FM-D-VS | 12 CONTACT(S), FEMALE, STRAIGHT TWO PART BOARD CONNECTOR, SURFACE MOUNT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SSTV16857MTDX_NL | 功能描述:寄存器 14-Bit Register with SSTL-2 Compatible I/O and Reset RoHS:否 制造商:NXP Semiconductors 逻辑类型:CMOS 逻辑系列:HC 电路数量:1 最大时钟频率:36 MHz 传播延迟时间: 高电平输出电流:- 7.8 mA 低电平输出电流:7.8 mA 电源电压-最大:6 V 最大工作温度:+ 125 C 封装 / 箱体:SOT-38 封装:Tube |

| SSTV16857TE-E | 制造商:Renesas Electronics Corporation 功能描述:14-BIT SSTL_2 REGISTERED BUFFER TSSOP 48 PIN - Tape and Reel |

| SSTV16859 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:2.5 V 13-bit to 26-bit SSTL_2 registered buffer for stacked DDR DIMM |

| SSTV16859_ZAA31162 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| SSTV16859_ZBA30062 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。