- 您现在的位置:买卖IC网 > PDF目录98143 > ST52F514G3B6 (STMICROELECTRONICS) 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP28 PDF资料下载

参数资料

| 型号: | ST52F514G3B6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP28 |

| 封装: | PLASTIC, DIP-28 |

| 文件页数: | 59/106页 |

| 文件大小: | 1340K |

| 代理商: | ST52F514G3B6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

8 FUZZY COMPUTATION (DP)

The ST52F510/F513/F514 Decision Processor

(DP) main features are:

s

Up to 8 Inputs with 8-bit resolution;

s

1 Kbyte of Program/Data Memory available to

store more than 300 to Membership Functions

(Mbfs) for each Input;

s

Up to 128 Outputs with 8-bit resolution;

s

Possibility of processing fuzzy rules with an

UNLIMITED number of antecedents;

s

UNLIMITED number of Rules and Fuzzy Blocks.

The limits on the number of Fuzzy Rules and

Fuzzy program blocks are only related to the

Program/Data Memory size.

8.1 Fuzzy Inference

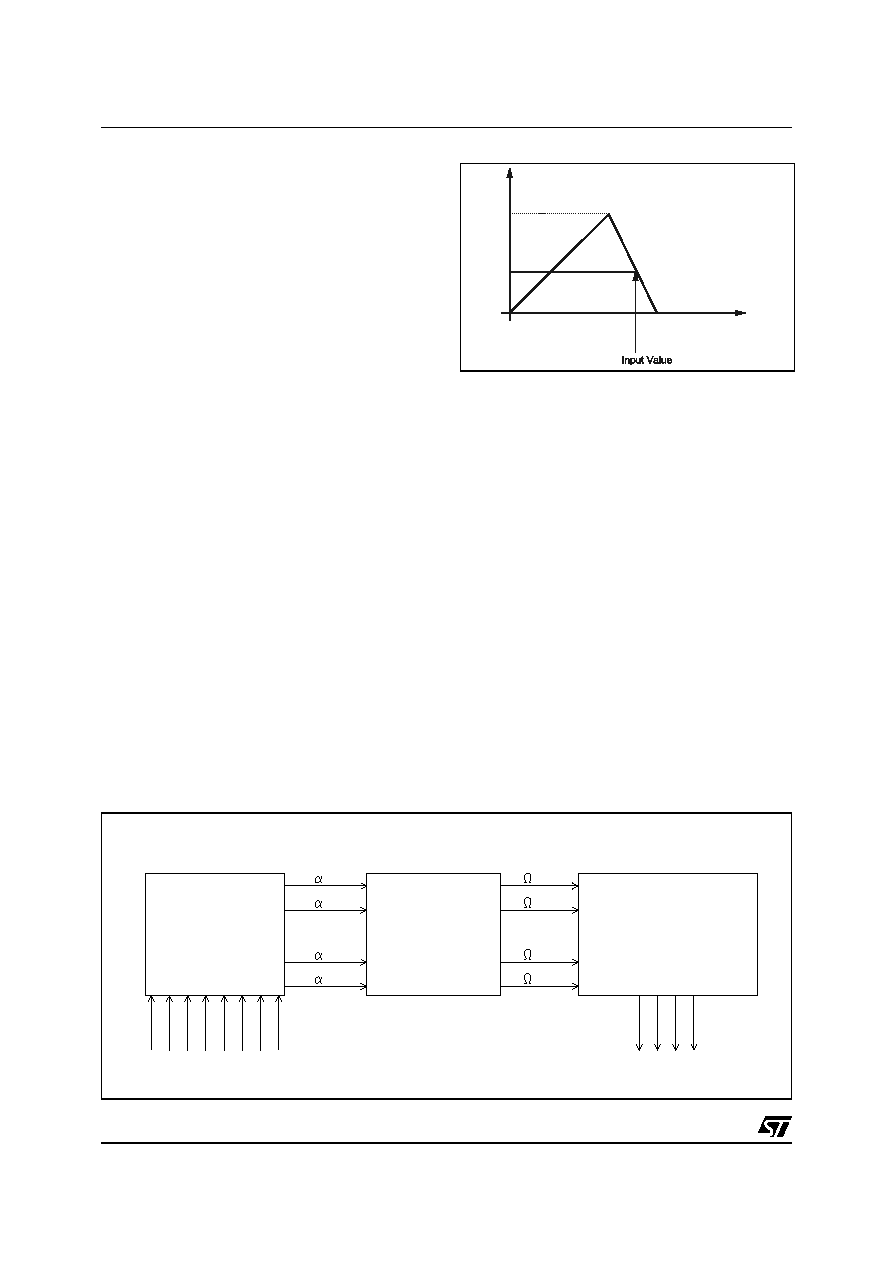

The block diagram shown in Figure 8.1 describes

the different steps performed during a Fuzzy

algorithm. The ST52F510/F513/F514 Core allows

for the implementation of a Mamdami type fuzzy

inference with crisp consequents. Inputs for fuzzy

inference are stored in 8 dedicated Fuzzy input

registers. The LDFR instruction is used to set the

Input Fuzzy registers with values stored in the

Register File. The result of a Fuzzy inference is

stored directly in a location of the Register File.

8.2 Fuzzyfication Phase

In this phase the intersection (alpha weight)

between the input values and the related Mbfs

(Figure 8.2) is performed.

Eight Fuzzy Input registers are available for Fuzzy

inferences.

Figure 8.1 Fuzzy Inference

Figure 8.2 Alpha Weight Calculation

After loading the input values by using the LDFR

assembler instruction, the user can start the fuzzy

inference

by

using

the

FUZZY

assembler

instruction. During fuzzyfication: input data is

transformed in the activation level (alpha weight) of

the Mbf’s.

8.3 Inference Phase

The Inference Phase manages the alpha weights

obtained during the fuzzyfication phase to compute

the truth value (

ω) for each rule.

This is a calculation of the maximum (for the OR

operator) and/or minimum (for the AND operator)

performed on alpha values according to the logical

connectives of Fuzzy Rules.

Several conditions may be linked together by

linguistic connectives AND/OR, NOT operators

and brackets.

The truth value

ω and the related output singleton

are used by the Defuzzyfication phase, in order

to complete the inference calculation.

11

1m

n1

nm

FUZZYFICATION

INFERENCE

PHASE

DEFUZZYFICATION

N rules

N rules -1

2

1

Input Values

Output Values

1

αij

j-th Mbf

i-th INPUT VARIABLE

相关PDF资料 |

PDF描述 |

|---|---|

| ST52F513G3B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP28 |

| ST52F513Y1B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP16 |

| ST52F513Y2B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP16 |

| ST52F510Y3B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP16 |

| ST52F514Y2B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST52F514G3M6 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microcontroller |

| ST52F514GMB6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

| ST52F514GMM6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

| ST52F514Y0B6 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microcontroller |

| ST52F514Y0M6 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microcontroller |

发布紧急采购,3分钟左右您将得到回复。