- 您现在的位置:买卖IC网 > PDF目录69351 > ST62P62CN1/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO16 PDF资料下载

参数资料

| 型号: | ST62P62CN1/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO16 |

| 封装: | PLASTIC, SSOP-16 |

| 文件页数: | 49/75页 |

| 文件大小: | 1753K |

| 代理商: | ST62P62CN1/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

53/75

ST6252C ST6262B ST6262C

INSTRUCTION SET (Cont’d)

Conditional Branch. The branch instructions

achieve a branch in the program when the select-

ed condition is met.

Bit Manipulation Instructions. These instruc-

tions can handle any bit in data space memory.

One group either sets or clears. The other group

(see Conditional Branch) performs the bit test

branch operations.

Control Instructions. The control instructions

control the MCU operations during program exe-

cution.

Jump and Call. These two instructions are used

to perform long (12-bit) jumps or subroutines call

inside the whole program space.

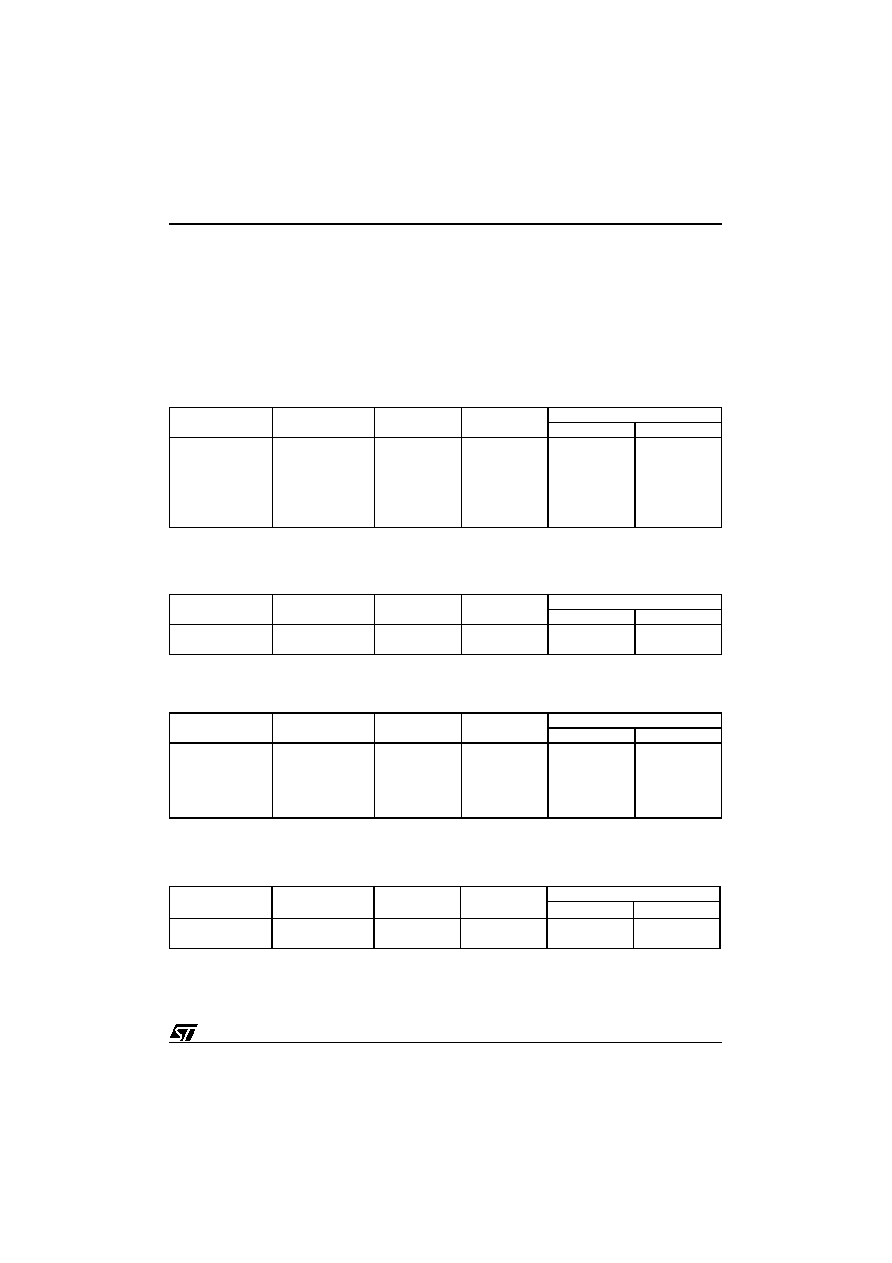

Table 18. Conditional Branch Instructions

Notes

:

b.

3-bit address

rr.

Data space register

e.

5 bit signed displacement in the range -15 to +16<F128M>

Δ . Affected. The tested bit is shifted into carry.

ee.

8 bit signed displacement in the range -126 to +129

* .

Not Affected

Table 19. Bit Manipulation Instructions

Notes:

b.

3-bit address;

* . Not<M> Affected

rr.

Data space register;

Table 20. Control Instructions

Notes:

1.

This instruction is deactivated<N>and a WAIT is automatically executed instead of a STOP if the watchdog function is selected.

Δ . Affected

*.

Not Affected

Table 21. Jump & Call Instructions

Notes:

abc. 12-bit address;

* .

Not Affected

Instruction

Branch If

Bytes

Cycles

Flags

Z

C

JRC e

C = 1

1

2

*

JRNC e

C = 0

1

2

*

JRZ e

Z = 1

1

2

*

JRNZ e

Z = 0

1

2

*

JRR b, rr, ee

Bit = 0

3

5

*

Δ

JRS b, rr, ee

Bit = 1

3

5

*

Δ

Instruction

Addressing Mode

Bytes

Cycles

Flags

Z

C

SET b,rr

Bit Direct

2

4

*

RES b,rr

Bit Direct

2

4

*

Instruction

Addressing Mode

Bytes

Cycles

Flags

Z

C

NOP

Inherent

1

2

*

RET

Inherent

1

2

*

RETI

Inherent

1

2

Δ

STOP (1)

Inherent

1

2

*

WAIT

Inherent

1

2

*

Instruction

Addressing Mode

Bytes

Cycles

Flags

Z

C

CALL abc

Extended

2

4

*

JP abc

Extended

2

4

*

相关PDF资料 |

PDF描述 |

|---|---|

| ST6252CN1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST72101G1M3/XXX | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO28 |

| ST72213G1M6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO28 |

| ST72213G1B3/XXX | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDIP32 |

| ST72213G1B1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST62P62CN6/MMMTR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CN6/MTFTR | 制造商:STMicroelectronics 功能描述: |

| ST62P65CM6/MRYTR | 制造商:STMicroelectronics 功能描述: |

| ST62P65CM6/RAL/TR | 制造商:STMicroelectronics 功能描述: |

| ST62P65CM6/RAP/TR | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。