- 您现在的位置:买卖IC网 > PDF目录69351 > ST62T32BB6 (STMICROELECTRONICS) 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, CDIP42 PDF资料下载

参数资料

| 型号: | ST62T32BB6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, CDIP42 |

| 封装: | CERAMIC, SDIP-42 |

| 文件页数: | 49/83页 |

| 文件大小: | 1815K |

| 代理商: | ST62T32BB6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

Obsolete

Product(s)

- Obsolete

Product(s)

Obsolete

Product(s)

- Obsolete

Product(s)

53/83

ST62T32B ST62E32B

4.3.5 CONTROL REGISTERS

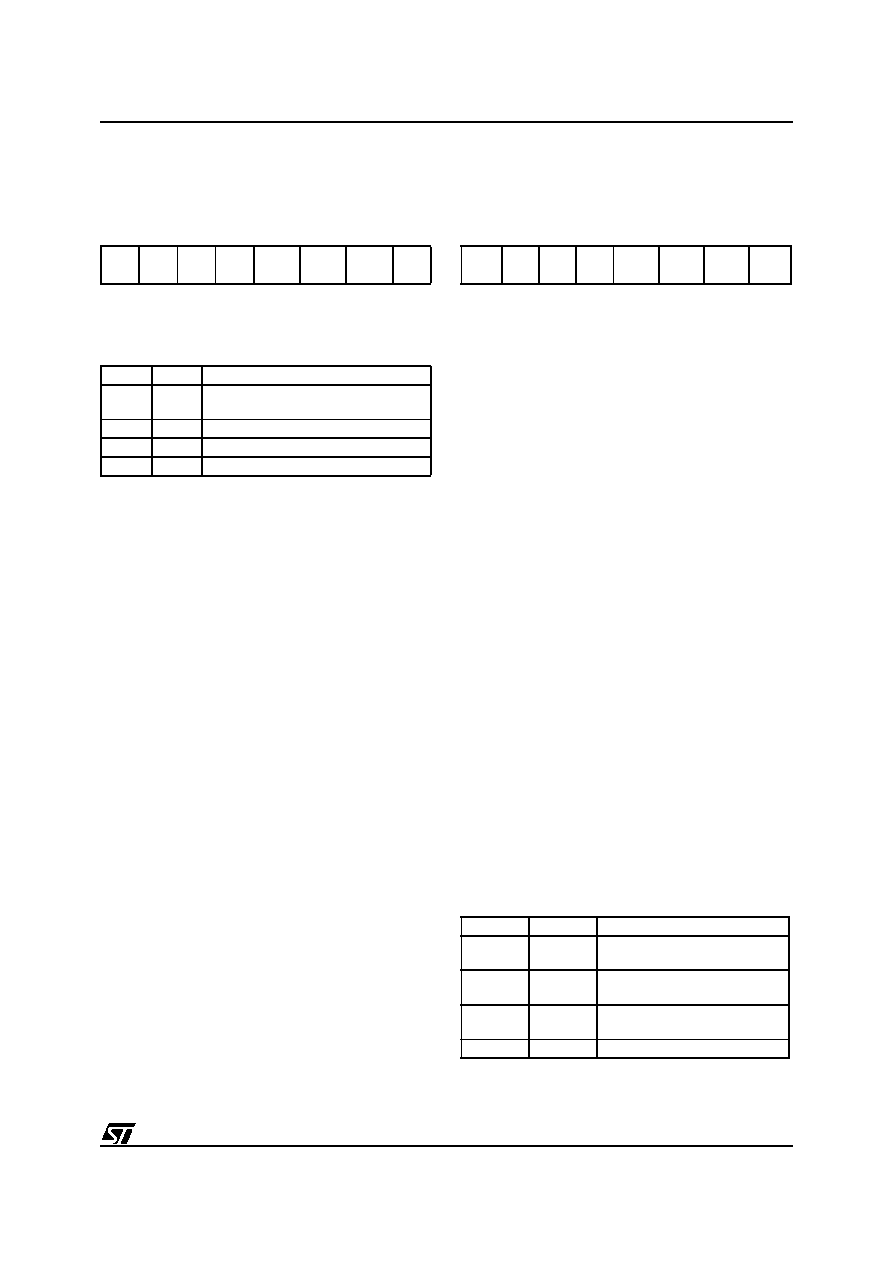

Status Control Register 1 (SCR1)

Address: E8h - Read/Write/Clear only

Bits 7 & 6 = PSC2..PSC1.

Clock Prescaler. These

bits define the prescaler options for the prescaler

to the Counter Register according to the following

table.

The Prescaler must be disabled (PSC2 = 0, PSC1

= 0) before a new prescaler factor is set if the

counter is running (after a hardware reset the

prescaler is automatically disabled).

To avoid inconsistencies in timing, the prescaler

factor should be set first, and then the counter

started.

Bit 5 = RELOAD. Reload enabled. When set this

bit enables reload from RLCP register into CT reg-

ister. On the contrary, if RELOAD is cleared,

RLCP is used as target for capture from the coun-

ter CT register.

Bit 4 = RUNRES.

Run/Reset. This bit enables the

RUN or RESET operation of the ARTIMER.

If 0, the counter CT is cleared to zero, and is

stopped. Setting this bit to 1 permits the startup of

the counter, and enables the synchronisation cir-

cuits for the timer inputs CP1 and CP2.

Bit 3 = OVFIEN.

Overflow Int. Enable. The Over-

flow Interrupt is masked when this bit is 0.

Setting the bit to 1 enables the overflow flag to set

the ARTIMER interrupt.

Bit 2 = OVFFLG. When this bit is 0, no overflow

has occurred since the last clear of this bit. If the

bit is at 1, an overflow has occurred.

This bit cannot be set by program, only cleared.

Bit 1 = OVFMD. The Overflow Output mode is set

by this bit; when 0, the overflow output is run in set

mode (OVF will be set on the first overflow event,

and will be reset when OVFFLG is cleared). When

1 the overflow output is in toggle mode; OVF tog-

gles its state on every overflow event (independ-

ent to the state of OVFFLG).

Bit 0 = This bit is reserved and must be set to 0.

Status Control Register 2 (SCR2)

Address: E1h - Read/Write/Clear only

Bit 7 = Reserved. Must be kept cleared.

Bit 6 = CP1ERR.

CP1 Error Flag. This bit is set to

1 if a new CP1 event has taken place since

CP1FLG was set to signal an error condition, it is 0

if there has been no event.

It is recommended to clear CP1ERR at any time

that CP1FLG is cleared, as further CP1 events

cannot be recognised if CP1ERR is set. This bit

cannot bet set by write, only cleared.

Bit 5 = CP2ERR.

CP1 Error Flag. This bit is set to

1 if a new CP2 event has taken place since

CP2FLG was set to signal an error condition, it is 0

if there has been no event.

It is recommended to clear CP2ERR at any time

that CP2FLG is cleared, as further CP2 events

cannot be recognised if CP2ERR is set. This bit

cannot bet set by write, only cleared.

Bit 4 = CP1IEN.

CP1 Interrupt Enable. CP1 The

Capture 1 Interrupt is masked when this bit is 0.

Setting the bit to 1 enables the CP1 event flag

CP1FLG to set the ARTIMER interrupt.

Bit 3 = CP1FLG.

CP1 Interrupt Flag. When this bit

is 0, no CP1 event has occurred since the last

clear of this bit. If the bit is at 1, a CP1 event has

occurred.

This bit cannot be set by program, only cleared.

Bit 2 = CP1POL.

CP1 Edge Polarity Select.

CP1POL defines the polarity for triggering the CP1

event.

A 0 defines the action on a falling edge on the CP1

input, a 1 on a rising edge.

Bit 1 & 0 = RLDSEL2..RLDSEL1.

Reload Source

Select. These bits define the source for the reload

events; they do not affect the operation of the cap-

ture modes.

70

PSC2

PSC1

RE-

LOAD

RUN-

RES

OVFIEN OVFFLG OVFMD

-

PSC2

PSC1

Function

00

Clock Disabled (prescaler and counter

stopped

0

1

Prescale by 1

1

0

Prescale by 4

1

Prescale by 16

70

-

CP1E

RR

CP2E

RR

CP1IE

N

CP1FLG CP1POL

RLDSEL

2

RLDSE

L1

RLDSEL2 RLDSEL1

Function

00

Reload and startup triggered by

RUNRES

01

Reload triggered by every CP1

event

10

Reload triggered by every CP2

event

1

Reload disabled

相关PDF资料 |

PDF描述 |

|---|---|

| ST62T32BB3 | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, CDIP42 |

| ST6232BB1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST6232BQ6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP42 |

| ST6232BQ3/XXX | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP42 |

| ST62T52BB6 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST62T32BQ6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K SPI/UAR RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST62T35BQ6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST62T40BQ6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST62T42BQ6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST62T45BQ6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。