- 您现在的位置:买卖IC网 > PDF目录385870 > ST63E69D1 (意法半导体) 8-BIT HCMOS MCU FOR DIGITAL CONTROLLED MULTI FREQUENCYMONITOR PDF资料下载

参数资料

| 型号: | ST63E69D1 |

| 厂商: | 意法半导体 |

| 英文描述: | 8-BIT HCMOS MCU FOR DIGITAL CONTROLLED MULTI FREQUENCYMONITOR |

| 中文描述: | 8位HCMOS单片机的数控多FREQUENCYMONITOR |

| 文件页数: | 46/71页 |

| 文件大小: | 584K |

| 代理商: | ST63E69D1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页

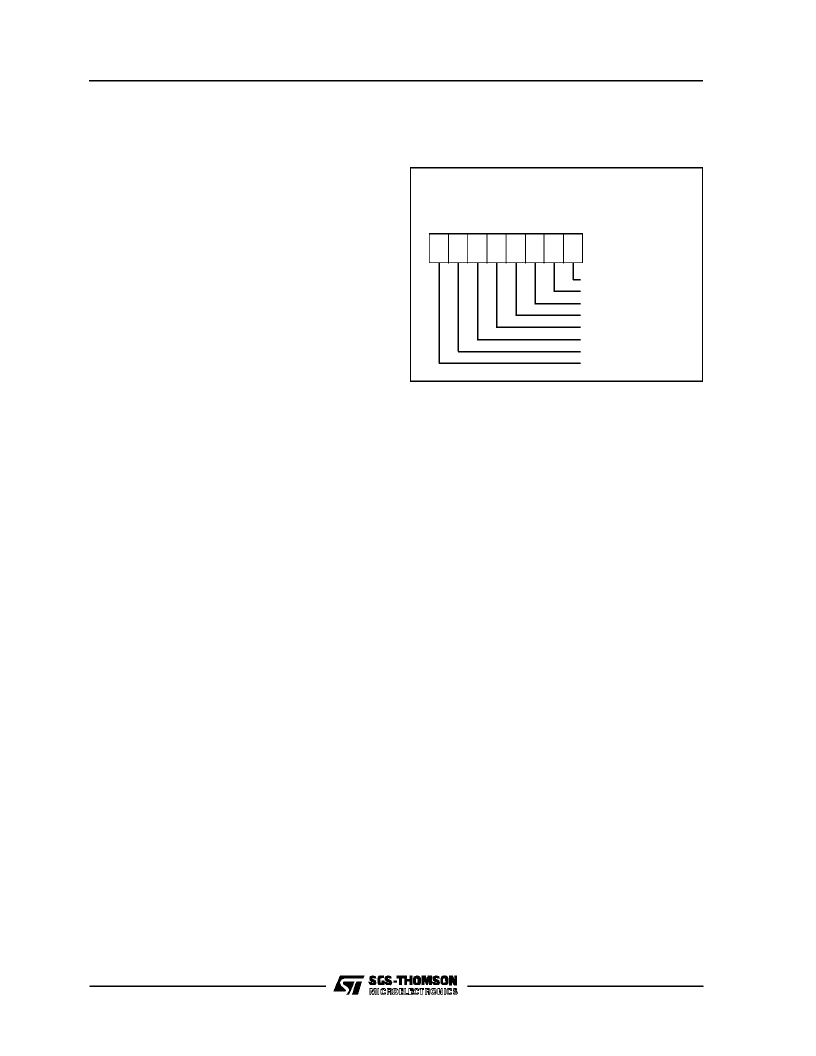

DLCR

DedicatedLatches Control

Register

(E9H, WriteOnly)

D7 D6 D5 D4 D3 D2 D1 D0

Unused

HSYEDGE

HSYINTEN

RESHSYLAT

PWREDGE

PWRINTEN

RESPWRLAT

Unused

Figure 55. DedicatedLatches Control Register

DEDICATED LATCHES

Two latchesare available which may generatein-

terrupts to the ST6369 core.

The HSYNC latch is set either by thefalling or ris-

ing edge ofthe signal on pin PC6(HSYNC). If bit 1

(HSYEDGE) of the latches register (E9H) is high,

then thelatch will betriggered on the rising edge of

the signal at PC6(HSYNC). Ifbit 1 (HSYEDGE)is

low, then the latch will be triggered on the falling

edge of the signal at PC6(HSYNC). The HSYNC

latch can be reset by settingbit3 (RESHSYLAT)of

the latches register; the bit is set only and a high

should be written every time the HSYNC latch

needs to be reset. If bit 2 (HSYINTEN) of the

latches register (E9H) is high, then the output of

the HSYNC latch, HSYNCN, may generate an in-

terrupt (#0). HSYNCN is inverted with respect to

the stateof the HSYNC latch. If bit 2 (HSYINTEN)

is low, then the output of the HSYNC latch,

HSYNCN, is forced high. The state of the HSYNC

latch may be read from bit 3 (HSYNC) of register

E4H; if the HSYNC latch is set, then bit 3 will be

high.

The PWR latch is set either by the falling or rising

edge of the signal on pin PC4(PWRIN). If bit 4

(PWREDGE) of the latches register(E9H) is high,

then thelatch will betriggered on the rising edge of

the signal at PC4(PWRIN). If bit 4 (PWREDGE) is

low, then the latch will be triggered on the falling

edge ofthe signal at PC4(PWRIN). The PWR latch

can be reset by setting bit6 (RESPWRLAT) of the

latches register; the bit is set only and a high

should be written everytime thePWR latch needs

to bereset. Ifbit5 (PWRINTEN) of thelatches reg-

ister (E9H) is high, then the output of the PWR

latch, PWRINTN, may generate an interrupt (#4).

PWRINTN is inverted with respect to the state of

the PWR latch. If bit 5 (PWRINTEN) is low, then

the output of the PWR latch, PWRINTN, is forced

high.

D0.

This bitis not used

D7

. This bit is not used

RESPWRLAT.

ResetsthePWRlatch;thisbitisset

only.

PWRINTEN.

Thisbit enablesthe PWRINTNsignal

(#4) fromthe latch to the ST6369 core. Undefined

after reset.

PWREDGE.

The bit determines the edge which

will cause the PWRIN latch to be set. If this bit is

high, thanthe PWRIN latch will be set on therising

edge of the PWRIN signal. Undefined after reset.

RESHSYLAT.

Resets the HSYNC latch; this bit is

set only.

HSYINTEN.

This bit enables the HSYNCN signal

(#0) fromthe latch to the ST6369 core. Undefined

after reset.

HSYEDGE.

The bitdeterminesthe edge whichwill

cause the HSYNC latch to be set. If thisbit is high,

than theHSYNClatch willbe setonthe rising edge

of the HSYNC signal.Undefinedafter reset.

ST6369

42/67

相关PDF资料 |

PDF描述 |

|---|---|

| ST700C12L0 | PHASE CONTROL THYRISTORS Hockey Puk Version |

| ST700C12L0L | PHASE CONTROL THYRISTORS Hockey Puk Version |

| ST700C12L1 | PHASE CONTROL THYRISTORS Hockey Puk Version |

| ST700C | PHASE CONTROL THYRISTORS Hockey Puk Version |

| ST700C12L2L | PHASE CONTROL THYRISTORS Hockey Puk Version |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST63E73J5D1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT ROM/OTP/EPROM MCUs FOR DIGITALLY CONTROLLED MULTISYNC/MULTISTANDARD MONITORS |

| ST63E85D1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCUs WITH ON-SCREEN-DISPLAY FOR TV TUNING |

| ST63E85D1/XX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| ST63E87D1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCUs WITH ON-SCREEN-DISPLAY FOR TV TUNING |

| ST63E87D1/XX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。