- 您现在的位置:买卖IC网 > PDF目录98144 > ST72311J2B6/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 PDF资料下载

参数资料

| 型号: | ST72311J2B6/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| 封装: | 0.600 INCH, SHRINK, PLASTIC, DIP-42 |

| 文件页数: | 66/92页 |

| 文件大小: | 624K |

| 代理商: | ST72311J2B6/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页当前第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

69/92

ST72311

SERIAL PERIPHERAL INTERFACE (Cont’d)

STATUS REGISTER (SR)

Read Only

Reset Value: 0000 0000 (00h)

Bit 7 = SPIF

Serial Peripheral data transfer flag.

This bit is set by hardware when a transfer has

been completed. An interrupt is generated if

SPIE=1 in the CR register. It is cleared by a soft-

ware sequence (an access to the SR register fol-

lowed by a read or write to the DR register).

0: Data transfer is in progress or has been ap-

proved by a clearing sequence.

1: Data transfer between the device and an exter-

nal device has been completed.

Note: While the SPIF bit is set, all writes to the DR

register are inhibited.

Bit 6 = WCOL

Write Collision status.

This bit is set by hardware when a write to the DR

register is done during a transmit sequence. It is

cleared by a software sequence (see Figure 40).

0: No write collision occurred

1: A write collision has been detected

Bit 5 = Unused.

Bit 4 = MODF

Mode Fault flag.

This bit is set by hardware when the SS pin is

pulled low in master mode (see Section 4.5.4.5

Master Mode Fault). An SPI interrupt can be gen-

erated if SPIE=1 in the CR register. This bit is

cleared by a software sequence (An access to the

SR register while MODF=1 followed by a write to

the CR register).

0: No master mode fault detected

1: A fault in master mode has been detected

Bits 3-0 = Unused.

DATA I/O REGISTER (DR)

Read/Write

Reset Value: Undefined

The DR register is used to transmit and receive

data on the serial bus. In the master device only a

write to this register will initiate transmission/re-

ception of another byte.

Notes: During the last clock cycle the SPIF bit is

set, a copy of the received data byte in the shift

register is moved to a buffer. When the user reads

the serial peripheral data I/O register, the buffer is

actually being read.

Warning: A write to the DR register places data di-

rectly into the shift register for transmission.

A read to the DR register returns the value located

in the buffer and not the contents of the shift regis-

ter (see Figure 37).

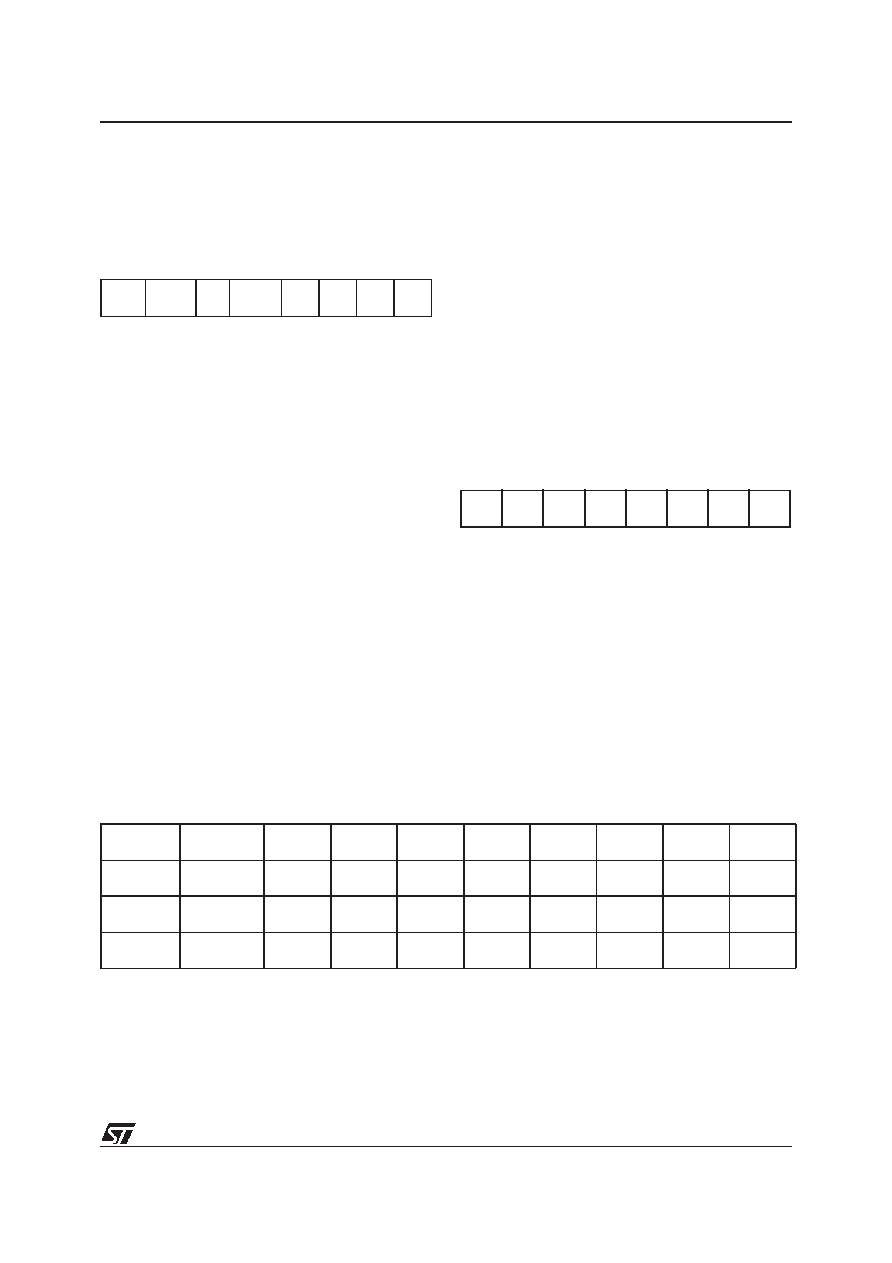

Table 19. SPI Register Map and Reset Values

70

SPIF

WCOL

-

MODF

-

70

D7

D6

D5

D4

D3

D2

D1

D0

Address

(Hex.)

Register

Name

76543210

21

DR

Reset Value

D7

x

D6

x

D5

x

D4

x

D3

x

D2

x

D1

x

D0

x

22

CR

Reset Value

SPIE

0

SPE

0

SPR2

0

MSTR

0

CPOL

x

CPHA

x

SPR1

x

SPR0

x

23

SR

Reset Value

SPIF

0

WCOL

0

-

0

MODF

0

-

0

-

0

-

0

-

0

69

相关PDF资料 |

PDF描述 |

|---|---|

| ST72311N2T3/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| ST72321BAR7T6 | MICROCONTROLLER, QFP64 |

| ST72321BR7T3 | MICROCONTROLLER, QFP64 |

| ST72321M9T3/XXX | 8-BIT, MROM, MICROCONTROLLER, PQFP80 |

| ST72321M7T5/XXX | 8-BIT, MROM, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST72311J2T1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH 8 TO 16K ROM/OTP/EPROM, 384 TO 512 BYTES RAM, ADC, WDG, SCI, SPI AND 2 TIMERS |

| ST72311J2T1/XXX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| ST72311J2T6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH 8 TO 16K ROM/OTP/EPROM, 384 TO 512 BYTES RAM, ADC, WDG, SCI, SPI AND 2 TIMERS |

| ST72311J2T6/XXX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| ST72311J2T6S | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH 8 TO 16K ROM/OTP/EPROM, 384 TO 512 BYTES RAM, ADC, WDG, SCI, SPI AND 2 TIMERS |

发布紧急采购,3分钟左右您将得到回复。