- 您现在的位置:买卖IC网 > PDF目录98145 > ST72652AR4T1/XXX (STMICROELECTRONICS) 8-BIT, MROM, MICROCONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | ST72652AR4T1/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, MICROCONTROLLER, PQFP64 |

| 封装: | 10 X 10 MM, ROHS COMPLIANT, TQFP-64 |

| 文件页数: | 126/161页 |

| 文件大小: | 2656K |

| 代理商: | ST72652AR4T1/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页当前第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页

ST72651AR6

67/161

Doc ID 7215 Rev 4

USB INTERFACE (Cont’d)

11.3.7 Register Description

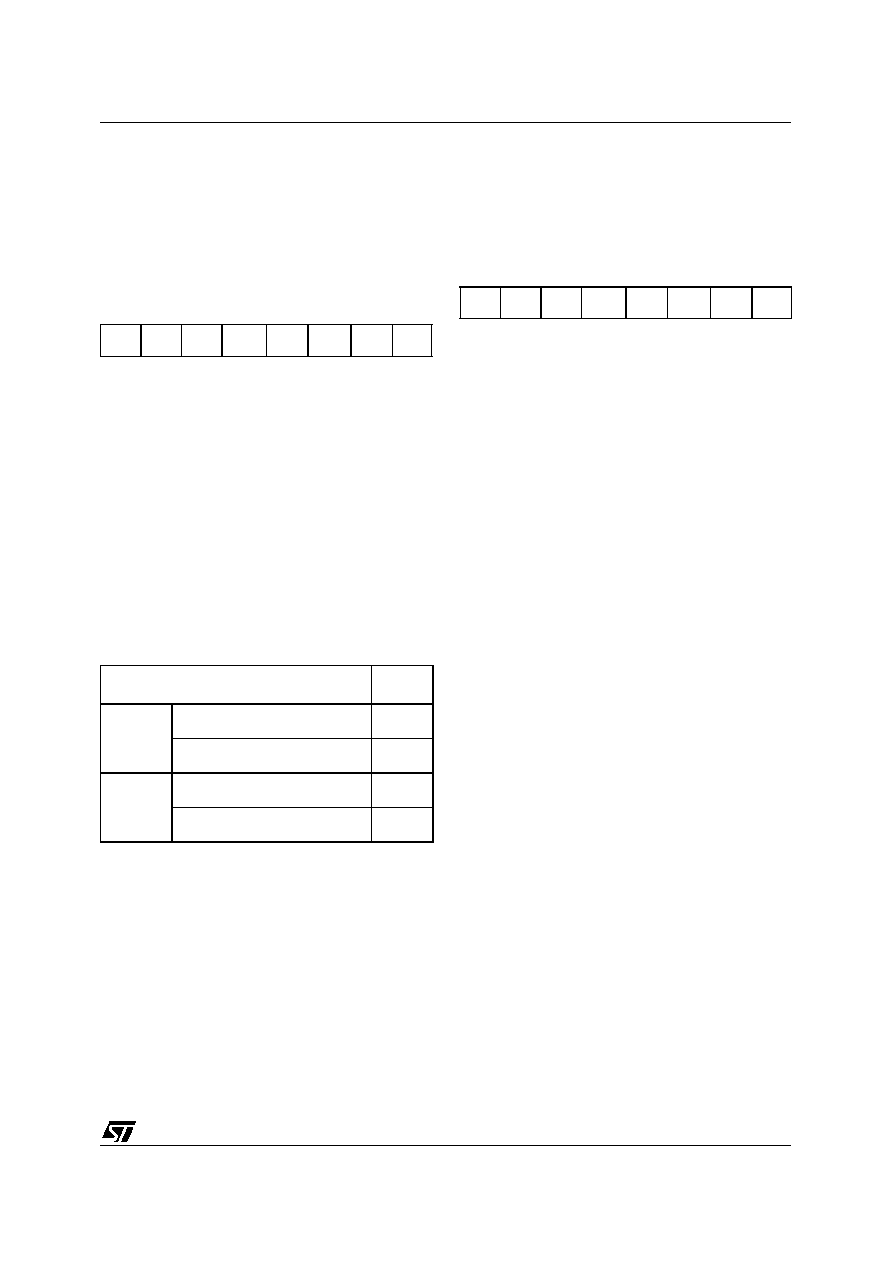

BUFFER

CONTROL/STATUS

REGISTER

(BUFCSR)

Read Only (except bit 0, read/write)

Reset Value: 0000 0000 (00h)

Bits 7:4 = Reserved, forced by hardware to 0.

Bit 3 = BUFNUM Current USB Buffer Number

This bit is set and cleared by hardware. When data

are received by Endpoint 2 in normal mode (refer

to the description of the MOD[1:0] bits in the

EP2RXR register) it indicates which buffer con-

tains the data.

0: Current buffer is Buffer 0

1: Current buffer is Buffer 1

Bits 2:1 = STATB[1:0] Buffer Status Bits

These bits are set and cleared by hardware. When

data are transmitted or received by Endpoint 2 in

upload or download mode (refer to the description

of the MOD[1:0] bits in the EP2RXR register) the

STATB[1:0] bits indicate the status as follows:

Bit 0 = CLR Clear Buffer Status

This bit is written by software to clear the BUF-

NUM and STATB[1:0] bits (it also resets the pack-

et counter of the Buffer Manager state machine). It

can be used to re-initialize the upload/download

flow (refer to the description of the MOD[1:0] bits in

the EP2RXR register).

0: No effect

1: Clear BUFNUM and STATB[1:0] bits

INTERRUPT STATUS REGISTER (ISTR)

Read/Write

Reset Value: 0000 0000 (00h)

These bits cannot be set by software. When an in-

terrupt occurs these bits are set by hardware. Soft-

ware must read them to determine the interrupt

type and clear them after servicing.

Note: The CTR bit (which is an OR of all the end-

point CTR flags) cannot be cleared directly, only

by clearing the CTR flags in the Endpoint regis-

ters.

Bit 7 = CTR Correct Transfer.

This bit is set by hardware when a correct transfer

operation is performed. This bit is an OR of all

CTR flags (CTR0 in the EP0R register and

CTR_RX and CTR_TX in the EPnR registers). By

looking in the USBSR register, the type of transfer

can be determined from the PID[1:0] bits for End-

point 0. For the other Endpoints, the Endpoint

number on which the transfer was made is identi-

fied by the EP[1:0] bits and the type of transfer by

the IN/OUT bit.

0: No Correct Transfer detected

1: Correct Transfer detected

Note: A transfer where the device sent a NAK or

STALL handshake is considered not correct (the

host only sends ACK handshakes). A transfer is

considered correct if there are no errors in the PID

and CRC fields, if the DATA0/DATA1 PID is sent

as expected, if there were no data overruns, bit

stuffing or framing errors.

Bit 6 = Reserved, forced by hardware to 0.

Bit 5 = SOVR Setup Overrun.

This bit is set by hardware when a correct Setup

transfer operation is performed while the software

is servicing an interrupt which occurred on the

same Endpoint (CTR0 bit in the EP0R register is

still set when SETUP correct transfer occurs).

0: No SETUP overrun detected

1: SETUP overrun detected

When this event occurs, the USBSR register is not

updated because the only source of the SOVR

event is the SETUP token reception on the Control

Endpoint (EP0).

70

000

0

BUF-

NUM

STAT

B1

STAT

B0

CLR

Meaning

STATBn

Value

Upload

Mode

Buffer n not full (USB waiting to

read Buffer n)

0

Buffer n full (USB can upload this

buffer)

1

Download

Mode

Buffer n empty (Can be written to

by USB)

0

Buffer n not empty (USB waiting

to write to this buffer)

1

70

CTR

0

SOVR ERROR SUSP ESUSP RESET SOF

1

相关PDF资料 |

PDF描述 |

|---|---|

| ST72651AR6T1E/XXX | 8-BIT, MROM, MICROCONTROLLER, PQFP64 |

| ST72652C4T1/XXX | 8-BIT, MROM, MICROCONTROLLER, PQFP48 |

| ST7267R8T1L/XXX | 16-BIT, MROM, 30 MHz, RISC MICROCONTROLLER, PQFP64 |

| ST7267C8T1/XXX | 16-BIT, MROM, 30 MHz, RISC MICROCONTROLLER, PQFP48 |

| ST72774S9T1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7265X-EVAL/MS | 制造商:STMicroelectronics 功能描述:ST6 EVAL BD - Bulk |

| ST7265X-EVAL/PFD | 制造商:STMicroelectronics 功能描述:USB FLASH EVAL - Bulk |

| ST7266 | 制造商:6940 功能描述:ST7266 |

| ST7267C8T1L | 制造商:STMicroelectronics 功能描述: |

| ST72681/R12 | 制造商:STMicroelectronics 功能描述:CONTROLLER FOR HIGH-PERFORMANCE BUS-POWERED USB 2.0 FLASH DR - Trays |

发布紧急采购,3分钟左右您将得到回复。