- 您现在的位置:买卖IC网 > PDF目录98145 > ST72P60E2M1 (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 PDF资料下载

参数资料

| 型号: | ST72P60E2M1 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 |

| 封装: | 0.300 INCH, LEAD FREE, PLASTIC, SOP-24 |

| 文件页数: | 81/118页 |

| 文件大小: | 2304K |

| 代理商: | ST72P60E2M1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页当前第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页

ST7260

65/117

SERIAL COMMUNICATIONS INTERFACE (Cont’d)

11.3.4.8 Clock Deviation Causes

The causes which contribute to the total deviation

are:

–DTRA: Deviation due to transmitter error (Local

oscillator error of the transmitter or the trans-

mitter is transmitting at a different baud rate).

–DQUANT: Error due to the baud rate quantisa-

tion of the receiver.

–DREC: Deviation of the local oscillator of the

receiver: This deviation can occur during the

reception of one complete SCI message as-

suming that the deviation has been compen-

sated at the beginning of the message.

–DTCL: Deviation due to the transmission line

(generally due to the transceivers)

All the deviations of the system should be added

and compared to the SCI clock tolerance:

DTRA + DQUANT + DREC + DTCL < 3.75%

11.3.4.9 Noise Error Causes

See also description of Noise error in Section

Start bit

The noise flag (NF) is set during start bit reception

if one of the following conditions occurs:

1. A valid falling edge is not detected. A falling

edge is considered to be valid if the 3 consecu-

tive samples before the falling edge occurs are

detected as '1' and, after the falling edge

occurs, during the sampling of the 16 samples,

if one of the samples numbered 3, 5 or 7 is

detected as a “1”.

2. During sampling of the 16 samples, if one of the

samples numbered 8, 9 or 10 is detected as a

“1”.

Therefore, a valid Start Bit must satisfy both the

above conditions to prevent the Noise Flag getting

set.

Data Bits

The noise flag (NF) is set during normal data bit re-

ception if the following condition occurs:

– During the sampling of 16 samples, if all three

samples numbered 8, 9 and10 are not the same.

The majority of the 8th, 9th and 10th samples is

considered as the bit value.

Therefore, a valid Data Bit must have samples 8, 9

and 10 at the same value to prevent the Noise

Flag getting set.

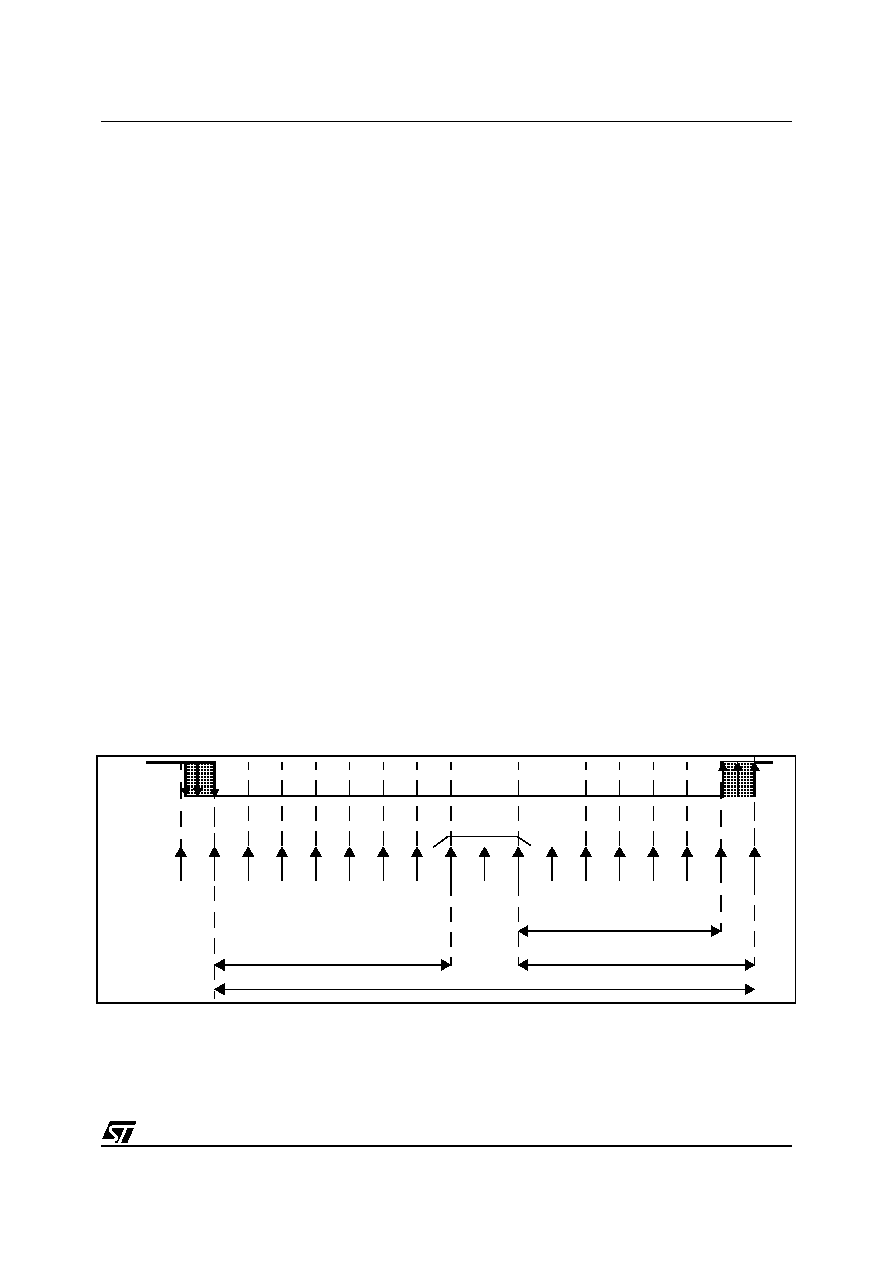

Figure 37. Bit Sampling in Reception Mode

RDI LINE

Sample

clock

12345678910

11

12

13

14

15

16

sampled values

One bit time

6/16

7/16

相关PDF资料 |

PDF描述 |

|---|---|

| ST7260E2M1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 |

| ST72T141K2M6XXX | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| ST72T141K2M3XXX | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| ST72T141K2MARE | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| ST7FL09Y0MATRE | 8-BIT, FLASH, 16 MHz, MICROCONTROLLER, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST72T101G1B6 | 功能描述:8位微控制器 -MCU OTP EPROM 4K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST72T101G1M6 | 功能描述:8位微控制器 -MCU OTP EPROM 4K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST72T101G2B6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST72T101G2M6 | 功能描述:8位微控制器 -MCU RO 511-ST72C104G2M6 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST72T121J2B6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K SPI/SCI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。