- 您现在的位置:买卖IC网 > PDF目录98146 > ST7PLITE05F0U6TR (STMICROELECTRONICS) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, QCC20 PDF资料下载

参数资料

| 型号: | ST7PLITE05F0U6TR |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, QCC20 |

| 封装: | QFN-20 |

| 文件页数: | 6/125页 |

| 文件大小: | 1956K |

| 代理商: | ST7PLITE05F0U6TR |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页

ST7LITE0x, ST7LITESx

103/125

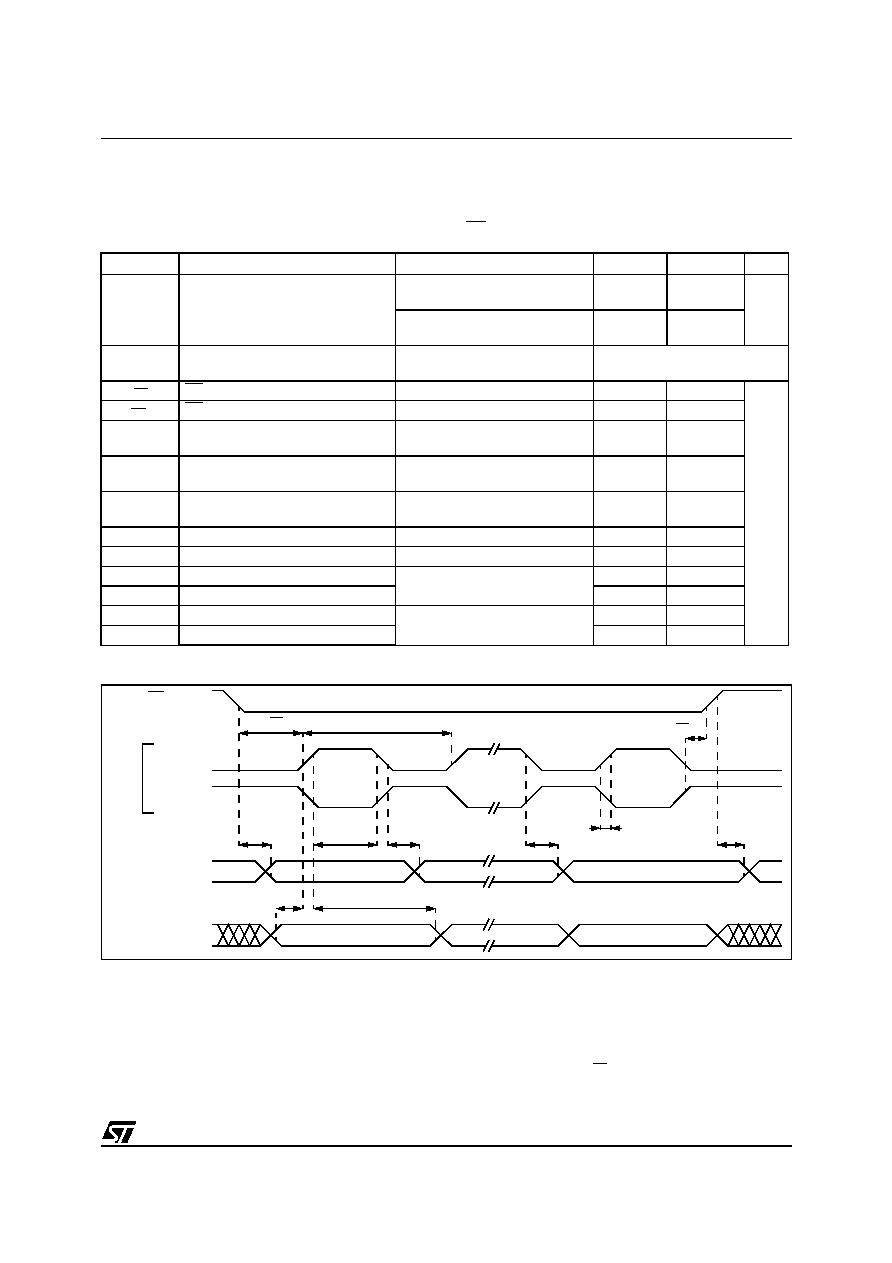

13.10 COMMUNICATION INTERFACE CHARACTERISTICS

13.10.1 SPI - Serial Peripheral Interface

Subject to general operating conditions for VDD,

fOSC, and TA unless otherwise specified.

Refer to I/O port characteristics for more details on

the input/output alternate function characteristics

(SS, SCK, MOSI, MISO).

Figure 77. SPI Slave Timing Diagram with CPHA=0 3)

Notes:

1. Data based on design simulation and/or characterisation results, not tested in production.

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has

its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

3. Measurement points are done at CMOS levels: 0.3xVDD and 0.7xVDD.

4. Depends on fCPU. For example, if fCPU=8MHz, then TCPU = 1/fCPU =125ns and tsu(SS)=175ns

Symbol

Parameter

Conditions

Min

Max

Unit

fSCK =

1/tc(SCK)

SPI clock frequency

Master

fCPU=8MHz

fCPU/128 =

0.0625

fCPU/4 =

2

MHz

Slave

fCPU=8MHz

0

fCPU/2 =

4

tr(SCK)

tf(SCK)

SPI clock rise and fall time

see I/O port pin description

tsu(SS)

1)

SS setup time 4)

Slave

TCPU + 50

ns

th(SS)

1)

SS hold time

Slave

120

tw(SCKH)

1)

tw(SCKL)

1)

SCK high and low time

Master

Slave

100

90

tsu(MI)

1)

tsu(SI)

1)

Data input setup time

Master

Slave

100

th(MI)

1)

th(SI)

1)

Data input hold time

Master

Slave

100

ta(SO)

1)

Data output access time

Slave

0

120

tdis(SO)

1)

Data output disable time

Slave

240

tv(SO)

1)

Data output valid time

Slave (after enable edge)

120

th(SO)

1)

Data output hold time

0

tv(MO)

1)

Data output valid time

Master (after enable edge)

120

th(MO)

1)

Data output hold time

0

SS INPUT

SC

K

INP

U

T

CPHA=0

MOSI INPUT

MISO OUTPUT

CPHA=0

tc(SCK)

tw(SCKH)

tw(SCKL)

tr(SCK)

tf(SCK)

tv(SO)

ta(SO)

tsu(SI)

th(SI)

MSB OUT

MSB IN

BIT6 OUT

LSB IN

LSB OUT

seenote2

CPOL=0

CPOL=1

tsu(SS)

th(SS)

tdis(SO)

th(SO)

see

note 2

BIT1 IN

相关PDF资料 |

PDF描述 |

|---|---|

| ST7PLITE05Y0B6 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP16 |

| ST7PLITE02F0U6TR | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, QCC20 |

| ST7PLITE02Y0B6 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP16 |

| ST7PLITE05Y0M3 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST7PLITE05Y0B3 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7PLITE05OBNTR | 制造商:STMicroelectronics 功能描述:MASKED ROM FOR MAGNA DONELLY - Tape and Reel |

| ST7PLITE05OBXTR | 制造商:STMicroelectronics 功能描述: |

| ST7PLITE05PBZTR | 制造商:STMicroelectronics 功能描述:MCU 8BIT ST7 CISC 1.5KB FLASH 2.5V/3.3V/5V 16SOIC - Tape and Reel |

| ST7PLITE05Y0B6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY, DATA EEPROM, ADC, TIMERS, SPI |

| ST7PLITE05Y0B6TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit microcontroller with single voltage Flash memory, data EEPROM, ADC, timers, SPI |

发布紧急采购,3分钟左右您将得到回复。