- 您现在的位置:买卖IC网 > PDF目录380730 > ST92163V (意法半导体) 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT PDF资料下载

参数资料

| 型号: | ST92163V |

| 厂商: | 意法半导体 |

| 英文描述: | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| 中文描述: | 16位产品全速USB微控制器16端点,20,000光盘和2K的RAM,I2C和脊髓损伤的复合设备, |

| 文件页数: | 170/224页 |

| 文件大小: | 1372K |

| 代理商: | ST92163V |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页当前第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页

170/224

ST92163 - SERIAL COMMUNICATIONS INTERFACE (SCI)

SERIAL COMMUNICATIONS INTERFACE

(Cont’d)

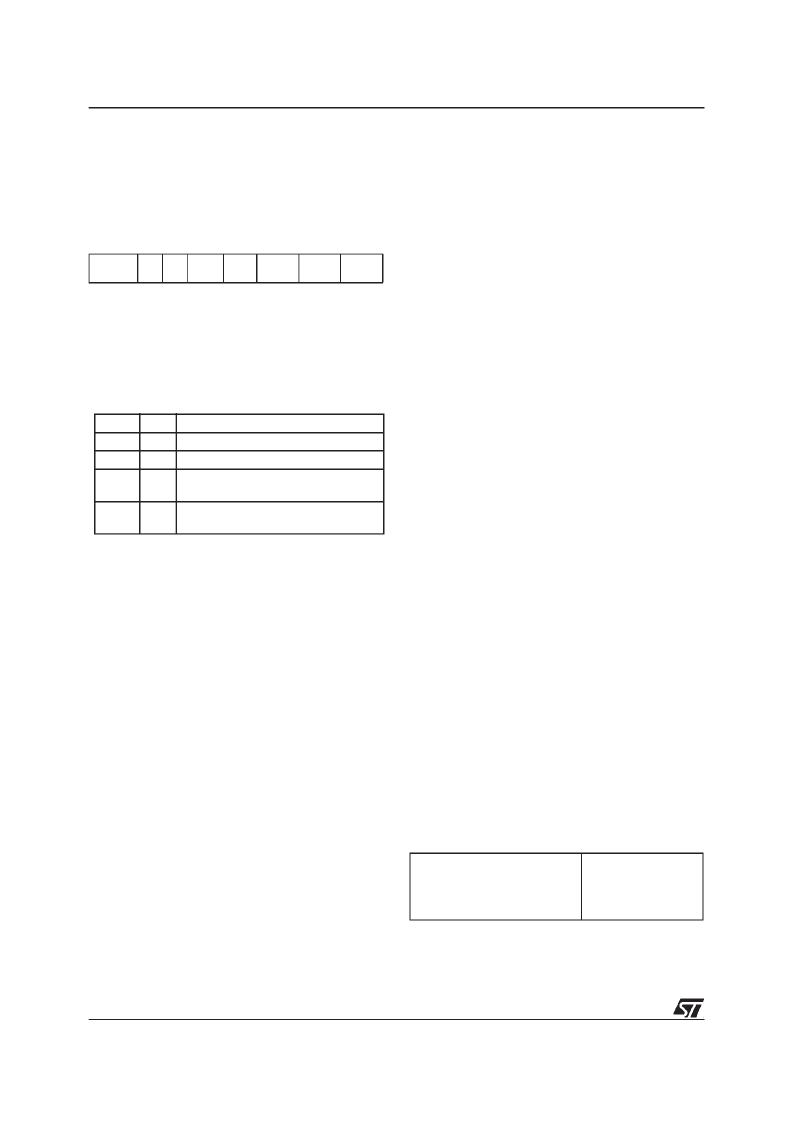

INTERRUPT/DMA PRIORITY REGISTER (IDPR)

R249 - Read/Write

Reset value: undefined

Bit 7 =

AMEN

: Address Mode Enable.

This bit, together with the AM bit (in the CHCR reg-

ister), decodes the desired addressing/9th data

bit/character match operation.

In Address modethe SCI monitors the input serial

data until its address is detected

Note:

Upon reception of address,the RXAP bit (in

the Interrupt Status Register) is set and an inter-

rupt cycle can begin. The address character will

not be transferred into the Receiver Buffer Regis-

ter but all data following the matched SCI address

and preceding thenext address word will be trans-

ferred to the Receiver Buffer Register and the

proper interrupts updated. If the address does not

match, all data following this unmatched address

will not be transferred to the Receiver Buffer Reg-

ister.

In any of the cases the RXAP bit must be reset by

software before the next word is transferred into

the Buffer Register.

When AMEN is reset and AM is set, a useful char-

acter searchfunction is performed. This allows the

SCI to generate an interrupt whenever a specific

character is encountered (e.g. Carriage Return).

Bit 6 =

SB

: Set Break

0: Stop the break transmission after minimum

break length.

1: Transmita break following thetransmission of all

data in the Transmitter Shift Register and the

Buffer Register.

Note:

Thebreak willbe a low level on the transmit-

ter data output for at least one complete word for-

mat. If software does not reset SB before the min-

imum break length has finished, the break condi-

tion will continue until software resets SB. TheSCI

terminates the break condition with a high level on

the transmitter data output for one transmission

clock period.

Bit 5 =

SA

: Set Address

If an address/9th data bit mode isselected, SA val-

ue will be loaded for transmission into the Shift

Register. This bit is cleared by hardware after its

load.

0: Indicate it is not an address word.

1: Indicate an address word.

Note:

Proper procedure would be, when the

Transmitter Buffer Register is empty, to load the

value of SA and then load the data into the Trans-

mitter Buffer Register.

Bit 4 =

RXD

: Receiver DMA Mask

This bit is reset by hardware when the transaction

counter value decrements to zero. At that time a

receiver End of Block interrupt can occur.

0: Disable Receiver DMA request(the RXDP bit in

the S_ISR register can request an interrupt).

1: Enable Receiver DMA request (the RXDP bit in

the S_ISR register can requesta DMAtransfer).

Bit 3 =

TXD

: Transmitter DMA Mask

This bit is reset by hardware when the transaction

counter value decrements to zero. At that time a

transmitter End Of Block interrupt can occur.

0: Disable Transmitter DMA request (TXBEM or

TXSEM bits in S_ISR can request an interrupt).

1: Enable Transmitter DMA request (TXBEM or

TXSEM bits in S_ISR can request a DMA trans-

fer).

Bit 2:0=

PRL[2:0]

: SCI Interrupt/DMAPriority bits

The

priority

for

the

(PRL2,PRL1,PRL0). Priority level 0 is the highest,

while level 7 represents no priority.

When the user has defined a priority level for the

SCI, priorities within the SCI are hardware defined.

These SCI internal priorities are:

SCI

is

encoded

with

7

0

AMEN

SB

SA

RXD

TXD

PRL2

PRL1

PRL0

AMEN

0

0

AM

0

1

Address interrupt if 9th data bit = 1

Address interrupt if character match

Address interrupt if character match

and 9th data bit =1

Address interrupt if character match

with word immediately following Break

1

0

1

1

Receiver DMA request

Transmitter DMA request

Receiver interrupt

Transmitter interrupt

highest priority

lowest priority

相关PDF资料 |

PDF描述 |

|---|---|

| ST92163N4G1 | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163N4G1E | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163N4G1L | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163N4G1V | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163N4D1 | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST92185 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16K/24K/32K ROM HCMOS MCU WITH ON-SCREEN-DISPLAY |

| ST92185B | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:16K/24K/32K ROM HCMOS MCU WITH ON-SCREEN-DISPLAY |

| ST92185B1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:16K/24K/32K ROM HCMOS MCU WITH ON-SCREEN-DISPLAY |

| ST92185B1BJ1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:16K/24K/32K ROM HCMOS MCU WITH ON-SCREEN-DISPLAY |

| ST92185B1BN1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:16K/24K/32K ROM HCMOS MCU WITH ON-SCREEN-DISPLAY |

发布紧急采购,3分钟左右您将得到回复。