参数资料

| 型号: | SY100E111AJI TR |

| 厂商: | Micrel Inc |

| 文件页数: | 5/6页 |

| 文件大小: | 0K |

| 描述: | IC CLK FANOUT BUFFER 1:9 28-PLCC |

| 标准包装: | 750 |

| 系列: | 100E, Precision Edge® |

| 类型: | 扇出缓冲器(分配) |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:9 |

| 差分 - 输入:输出: | 是/是 |

| 输入: | PECL |

| 输出: | PECL |

| 电源电压: | 4.2 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC |

| 包装: | 带卷 (TR) |

| 其它名称: | SY100E111AJITR SY100E111AJITR-ND |

Micrel, Inc

SY88933AL

February 2007

5

M9999-021207-B

hbwhelp@micrel.com or (408) 955-1690

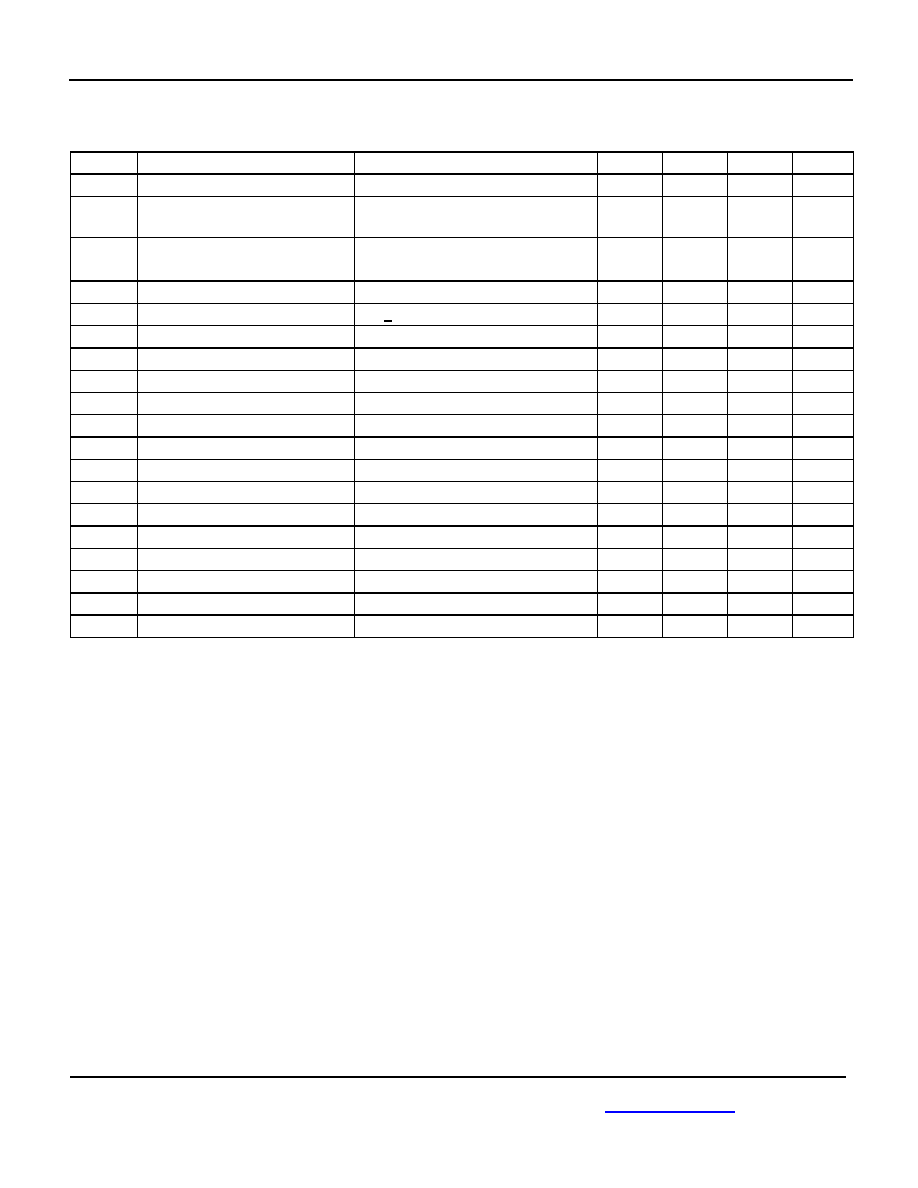

AC Electrical Characteristics

VCC = 3.0V to 3.6V; RLOAD = 50 to VCC–2V; TA = –40°C to +85°C; typical values at VCC = +3.3V, TA = +25

oC.

Symbol

Parameter

Condition

Min

Typ

Max

Units

PSRR

Power Supply Rejection Ratio

35

dB

tr, tf

Output Rise/Fall Time

(20% to 80%)

Note 3

260

ps

tJITTER

Deterministic

Random

Note 4

Note 5

15

5

pspp

psRMS

VID

Differential Input Voltage Swing

Figure 1

5

1800

mVpp

VOD

Differential Output Voltage Swing

VID > 18mVpp, Figure 1

1500

mVpp

TOFF

SD Release Time

2

10

s

TON

SD Assert Time

2

10

s

SDAL

Low SD Assert Level

RSDLVL = 15k, Note 6

3.4

6.5

mVpp

SDDL

Low SD De-assert Level

RSDLVL = 15k, Note 6

1.0

2.3

mVpp

HYSL

Low SD Hysteresis

RSDLVL = 15k, Note 7

1

3.4

4.5

dB

SDAM

Medium SD Assert Level

RSDLVL = 5k, Note 6

6.2

8

mVpp

SDDM

Medium SD De-assert Level

RSDLVL = 5k, Note 6

3

4.2

mVpp

HYSM

Medium SD Hysteresis

RSDLVL = 5k, Note 7

2

3.4

4.5

dB

SDAH

High SD Assert Level

RSDLVL = 100, Note 6

16.4

20

mVpp

SDDH

High SD De-assert Level

RSDLVL = 100, Note 6

8

10.8

mVpp

HYSH

High SD Hysteresis

RSDLVL = 100, Note 7

2

3.4

4.5

dB

B-3dB

3dB Bandwidth

1

GHz

AV(Diff)

Differential Voltage Gain

42

dB

S21

Single-Ended Small-Signal Gain

30

36

dB

Notes:

3. Amplifier in limiting mode. Input is a 200MHz square wave.

4. Deterministic jitter measured using 1.25Gbps K28.5 pattern, VID = 10mVpp.

5. Random jitter measured using 1.25Gbps K28.7 pattern, VID = 10mVpp.

6. See “Typical Operating Characteristics” for a graph showing how to choose a particular RSDLVL for a particular SD assert and

its associated de-assert amplitude.

7. This specification defines electrical hysteresis as 20log (SD Assert/SD De-assert). The ratio between optical hysteresis and

electrical hysteresis is found to vary between 1.5 and 2 depending upon the level of received optical power and ROSA

characteristics. Based on that ratio, the optical hysteresis corresponding to the electrical hysteresis range 1dB-4.5 dB, shown

in the AC characteristics table, will be 0.5dB-3dB optical hysteresis

相关PDF资料 |

PDF描述 |

|---|---|

| V300A48H500BG2 | CONVERTER MOD DC/DC 48V 500W |

| SY100E111AJI | IC CLK FANOUT BUFFER 1:9 28-PLCC |

| V300A48H500BG | CONVERTER MOD DC/DC 48V 500W |

| SY100E111AJC TR | IC CLK FANOUT BUFFER 1:9 28-PLCC |

| SY100E111AJC | IC CLK FANOUT BUFFER 1:9 28-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY100E111AJY | 功能描述:缓冲器和线路驱动器 5V 1:9 Differential Clock Driver (without Enable) (I Temp, Lead Free) RoHS:否 制造商:Micrel 输入线路数量:1 输出线路数量:2 极性:Non-Inverting 电源电压-最大:+/- 5.5 V 电源电压-最小:+/- 2.37 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Reel |

| SY100E111AJY TR | 功能描述:缓冲器和线路驱动器 5V 1:9 Differential Clock Driver (without Enable) (I Temp, Lead Free) RoHS:否 制造商:Micrel 输入线路数量:1 输出线路数量:2 极性:Non-Inverting 电源电压-最大:+/- 5.5 V 电源电压-最小:+/- 2.37 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Reel |

| SY100E111AJYTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:5V/3.3V 1:9 DIFFERENTIAL CLOCK DRIVER (w/o ENABLE) |

| SY100E111JC | 功能描述:IC CLK FANOUT BUFFER 1:9 28-PLCC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:100E, ECLinPS™ 标准包装:1 系列:HiPerClockS™ 类型:扇出缓冲器(分配),多路复用器 电路数:1 比率 - 输入:输出:2:18 差分 - 输入:输出:是/无 输入:CML,LVCMOS,LVPECL,LVTTL,SSTL 输出:LVCMOS,LVTTL 频率 - 最大:250MHz 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:- 其它名称:800-1923-6 |

| SY100E111JC TR | 功能描述:IC CLK FANOUT BUFFER 1:9 28-PLCC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:100E, ECLinPS™ 标准包装:1 系列:HiPerClockS™ 类型:扇出缓冲器(分配),多路复用器 电路数:1 比率 - 输入:输出:2:18 差分 - 输入:输出:是/无 输入:CML,LVCMOS,LVPECL,LVTTL,SSTL 输出:LVCMOS,LVTTL 频率 - 最大:250MHz 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:- 其它名称:800-1923-6 |

发布紧急采购,3分钟左右您将得到回复。