参数资料

| 型号: | SY100E195JY |

| 厂商: | Micrel Inc |

| 文件页数: | 6/8页 |

| 文件大小: | 0K |

| 描述: | IC DELAY LINE 128TAP 28-PLCC |

| 标准包装: | 38 |

| 系列: | 100E, Precision Edge® |

| 标片/步级数: | 128 |

| 功能: | 可编程 |

| 延迟到第一抽头: | 1.39ns |

| 接头增量: | 20ps |

| 可用的总延迟: | 1.39ns ~ 3.63ns |

| 独立延迟数: | 1 |

| 电源电压: | -4.2 V ~ -5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC |

| 包装: | 管件 |

| 其它名称: | 576-2440 SY100E195JY-ND |

6

Precison Edge

SY10E195

SY100E195

Micrel, Inc.

M9999-032006

hbwhelp@micrel.com or (408) 955-1690

APPLICATIONS INFORMATION

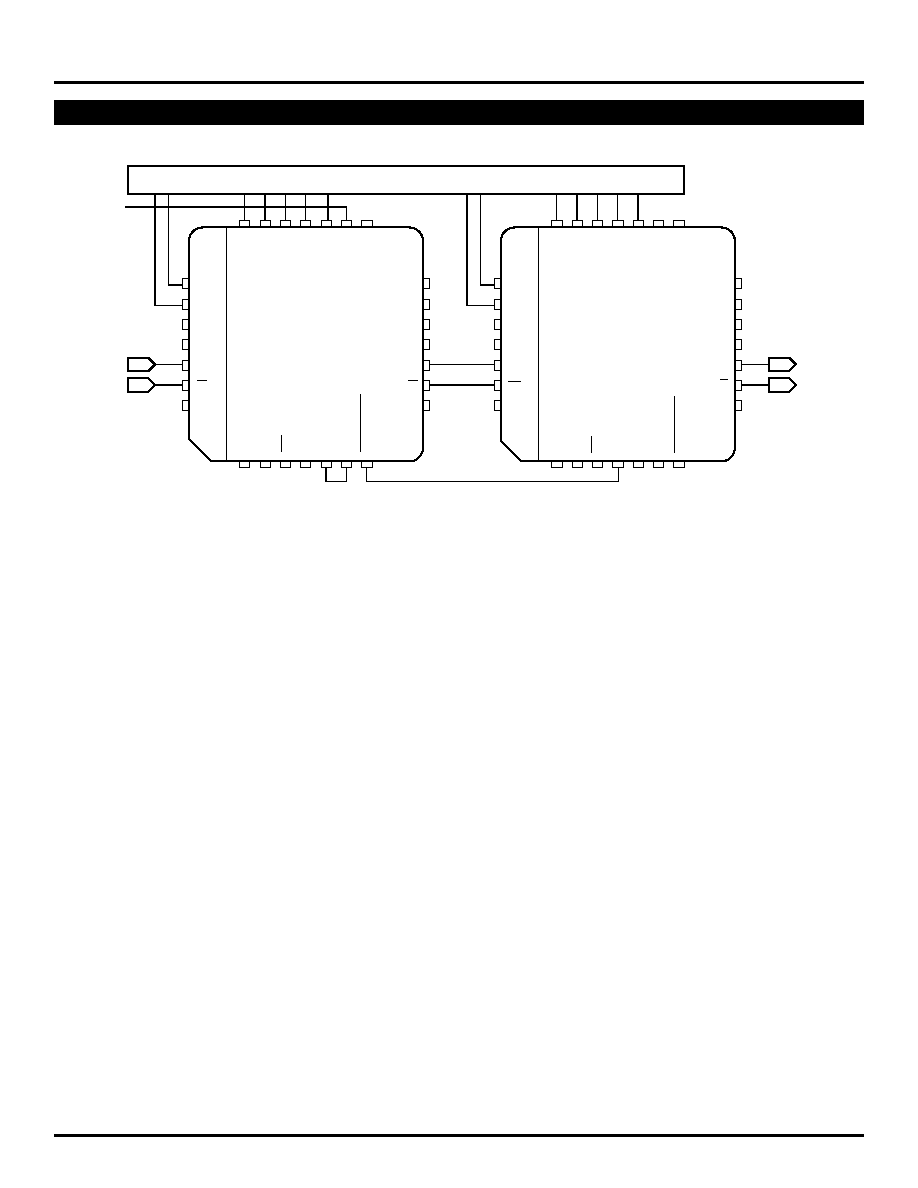

Cascading Multiple E195s

To increase the programmable range of the E195,

internal cascade circuitry has been included. This circuitry

allows for the cascading of multiple E195s without the

need for any external gating. Furthermore, this capability

requires only one more address line per added E195.

Obviously, cascading multiple PDCs will result in a larger

programmable range; however, this increase is at the

expense of a longer minimum delay.

Figure 1 illustrates the interconnect scheme for

cascading two E195s. As can be seen, this scheme can

easily be expanded for larger E195 chains. The D7 input

of the E195 is the cascade control pin.

With the

interconnect scheme of Figure 1, when D7 is asserted, it

signals the need for a larger programmable range than

is achievable with a single device.

An expansion of the latch section of the block diagram

is pictured below. Use of this diagram will simplify the

explanation of how the cascade circuitry works. When

D7 of chip #1 above is low, the cascade output will also

be low, while the cascade bar output will be a logical

high. In this condition, the SET MIN pin of chip #2 will

be asserted and, thus, all of the latches of chip #2 will

be reset and the device will be set at its minimum delay.

Since the RESET and SET inputs of the latches are

overriding, any changes on the A0–A6 address bus will

not affect the operation of chip #2.

Chip #1, on the other hand, will have both SET MIN

and SET MAX de-asserted so that its delay will be

controlled entirely by the address bus A0–A6. If the delay

needed is greater than can be achieved with 31.75 gate

delays (1111111 on the A0–A6 address bus), D7 will be

asserted to signal the need to cascade the delay to the

next E195 device. When D7 is asserted, the SET MIN

pin of chip #2 will be de-asserted and the delay will be

controlled by the A0–A6 address bus. Chip #1, on the

other hand, will have its SET MAX pin asserted, resulting

in the device delay to be independent of the A0–A6

address bus.

When the SET MAX pin of chip #1 is asserted, the D0

and D1 latches will be reset while the rest of the latches

will be set.

In addition, to maintain monotonicity, an

additional gate delay is selected in the cascade circuitry.

As a result, when D7 of chip #1 is asserted, the delay

increases from 31.75 gates to 32 gates. A 32-gate delay

is the maximum delay setting for the E195.

To expand this cascading scheme to more devices,

one simply needs to connect the D7 input and CASCADE

outputs of the current most significant E195 to the new

most significant E195 in the same manner as pictured in

Figure 1. The only addition to the logic is the increase

of one line to the address bus for cascade control of the

second PDC.

Figure 1. Cascading Interconnect Architecture

E196

Chip #1

D

4

D

5

D

6

D

7

D

2

D

3

D1

D0

LEN

VEE

IN

VBB

IN

SET

MIN

SET

MAX

CASCADE

EN

CASCADE

VCC

VCCO

Q

VCCO

Q

E196

Chip #2

D

4

D

5

D

6

D

7

D

2

D

3

D1

D0

LEN

VEE

IN

VBB

IN

SET

MIN

SET

MAX

CASCADE

EN

CASCADE

VCC

VCCO

Q

VCCO

Q

ADDRESS BUS (A0 – A6)

A7

Input

Output

相关PDF资料 |

PDF描述 |

|---|---|

| DS1023S-100+ | IC DELAY LINE 256TAP 16-SOIC |

| VE-2WK-MW | CONVERTER MOD DC/DC 40V 100W |

| DS1100LU-20+ | IC DELAY LINE 5TAP 20NS 8-USOP |

| DS1023S-500+ | IC DELAY LINE 256TAP 16-SOIC |

| VE-BWB-MV | CONVERTER MOD DC/DC 95V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY100E195JY TR | 功能描述:IC DELAY LINE 128TAP 28-PLCC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:100E, Precision Edge® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR) |

| SY100E195JYTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:PROGRAMMABLE DELAY CHIP |

| SY100E196 | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:PROGRAMMABLE DELAY CHIP WITH ANALOG INPUT |

| SY100E196JC | 功能描述:IC DELAY LINE 7TAP 28-PLCC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:100E, Precision Edge® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR) |

| SY100E196JCTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:PROGRAMMABLE DELAY CHIP WITH ANALOG INPUT |

发布紧急采购,3分钟左右您将得到回复。