- 您现在的位置:买卖IC网 > PDF目录98149 > SY100EP196VTC (MICREL INC) ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 PDF资料下载

参数资料

| 型号: | SY100EP196VTC |

| 厂商: | MICREL INC |

| 元件分类: | 延迟线 |

| 英文描述: | ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 |

| 封装: | TQFP-32 |

| 文件页数: | 7/18页 |

| 文件大小: | 179K |

| 代理商: | SY100EP196VTC |

15

ECL Pro

SY100EP196V

Micrel

For best performance, use good high frequency layout

techniques, filter V

CC supplies, and keep ground connections

short. Use multiple vias where possible. Also, use controlled

impedance transmission lines to interface with the

SY100EP196V data inputs and outputs.

V

BB Supply

The V

BB pin is an internally generated supply, and is

available for use only by the SY100EP196V. When unused,

this pin should be left unconnected. The two common uses

for V

BB are to handle a single-ended PECL input, and to re-

bias inputs for AC coupling applications.

If IN, /IN is driven by a single-ended output, V

BB is used

to bias the unused input. Please refer to Figures 9. The

PECL signal driving SY100EP196V may optionally be

inverted in this case.

When the signal is AC coupled, V

BB is used, as shown in

Figure 10, to re-bias IN, /IN. This ensures that SY100EP196V

inputs are within its acceptable common mode range.

In all cases, V

BB current sinking or sourcing must be

limited to 0.5mA or less.

APPLICATIONS INFORMATION

Setting D Input Logic Thresholds

As explained earlier, in all designs where the

SY100EP196V V

EE supply is at zero volts, the D inputs

may accommodate CMOS and TTL level signals, as well as

PECL or LVPECL. Figures 9 show how to connect V

CF and

V

EF for all possible cases.

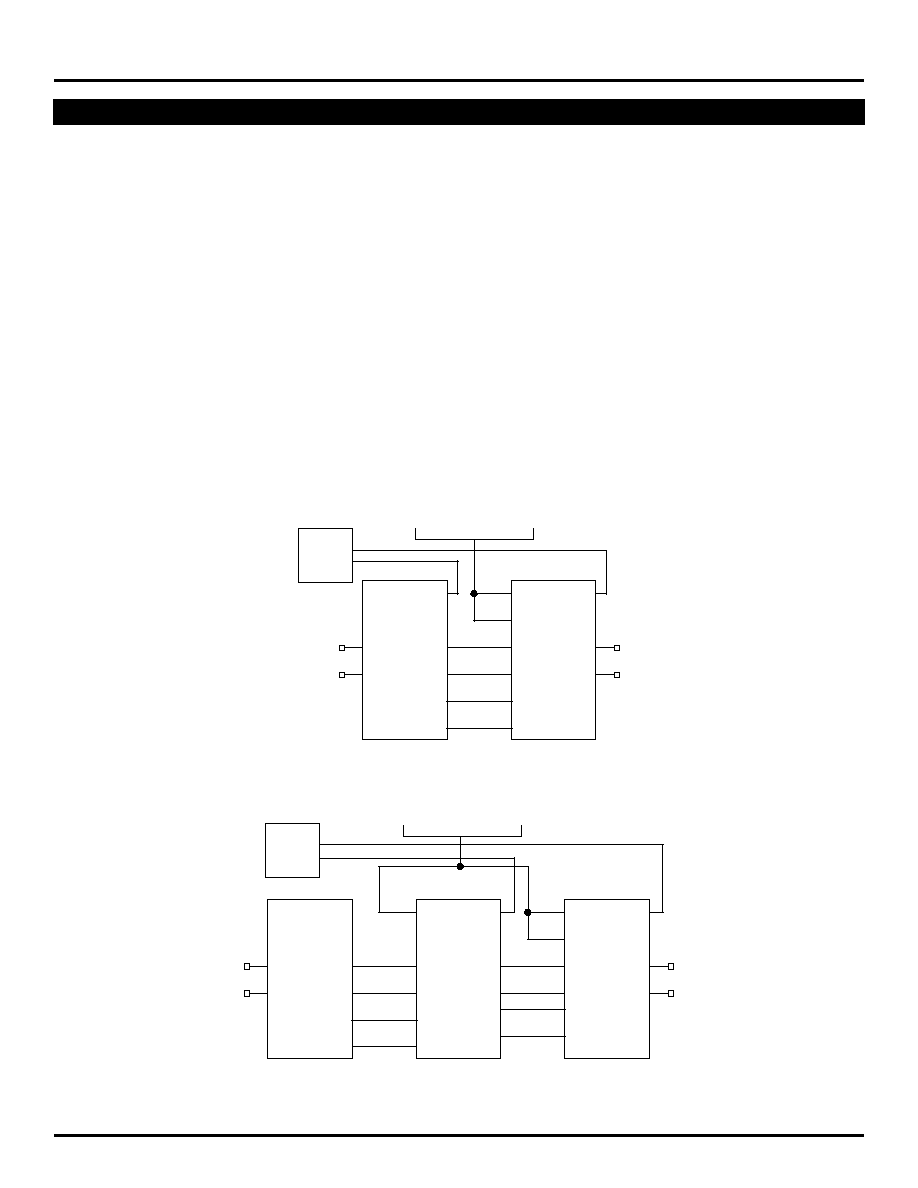

Cascading

Two or more SY100EP196V may be cascaded, in order

to extend the range of delays permitted. Each additional

SY100EP196V adds about 2200ps to the minimum delay,

and adds another 10240ps to the delay range.

Internal cascade circuitry has been included in the

SY100EP196V. Using this internal circuitry, SY100EP196V

may be cascaded without any external gating.

Examples of cascading 2, 3, or 4 SY100EP196V appear

in Figures 10. Table 7 lists the nominal delay for all the

cases that appear in Figures 10.

IN

/IN

Q

/Q

IN

/IN

Q

FTUNE

/Q

D[9:0]

SY100EP196V

#2

#1

SETMIN

SETMAX

/CASCADE

CASCADE

D[10]

C[9:0]

C[10]

Control Word (11bits)

DAC

Figure 10a. Cascading Two SY100EP196V

IN

/IN

Q

/Q

IN

/IN

Q

/Q

SY100EP196V

#3

DAC

#2

SETMIN

SETMAX

SETMIN

SETMAX

/CASCADE

CASCADE

D[10]

C[11]

IN

/IN

Q

FTUNE

/Q

D[9:0]

SY100EP196V

#1

/CASCADE

CASCADE

D[10]

C[9:0]

C[10]

Control Word (12bits)

Figure 10b. Cascading Three SY100EP196V

相关PDF资料 |

PDF描述 |

|---|---|

| SY100S336AJC | 100S SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, PQCC28 |

| SY100S336AFC | 100S SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CQFP24 |

| SY100S336DC | 100S SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDIP24 |

| SY54017ARMGTR | 54017 SERIES, 2 LINE TO 1 LINE MULTIPLEXER, COMPLEMENTARY OUTPUT, QCC16 |

| SY54020ARMGTR | LOW SKEW CLOCK DRIVER, QCC16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY100EP196VTG | 功能描述:延迟线/计时元素 3.3V/5V 2.5 GHz Programmable Delay Line w/Fine Tune (I Temp, Green) RoHS:否 制造商:Micrel 功能:Active Programmable Delay Line 传播延迟时间:1000 ps 工作温度范围: 封装 / 箱体:QFN-24 封装:Tube |

| SY100EP196VTG TR | 功能描述:延迟线/计时元素 3.3V/5V 2.5 GHz Programmable Delay Line w/Fine Tune (I Temp, Green) RoHS:否 制造商:Micrel 功能:Active Programmable Delay Line 传播延迟时间:1000 ps 工作温度范围: 封装 / 箱体:QFN-24 封装:Tube |

| SY100EP196VTI | 功能描述:IC DELAY LINE 1024TAP 32-TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:100EP, ECL Pro® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR) |

| SY100EP196VTI TR | 功能描述:IC DELAY LINE 1024TAP 32-TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:100EP, ECL Pro® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR) |

| SY100EP210UTG | 功能描述:缓冲器和线路驱动器 2.5-5V Dual 1:5 PECL Fanout Buffer (I Temp, Green) RoHS:否 制造商:Micrel 输入线路数量:1 输出线路数量:2 极性:Non-Inverting 电源电压-最大:+/- 5.5 V 电源电压-最小:+/- 2.37 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。