- 您现在的位置:买卖IC网 > PDF目录98149 > SY100EP196VTCTR (MICREL INC) ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 PDF资料下载

参数资料

| 型号: | SY100EP196VTCTR |

| 厂商: | MICREL INC |

| 元件分类: | 延迟线 |

| 英文描述: | ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 |

| 封装: | TQFP-32 |

| 文件页数: | 12/18页 |

| 文件大小: | 179K |

| 代理商: | SY100EP196VTCTR |

3

ECL Pro

SY100EP196V

Micrel

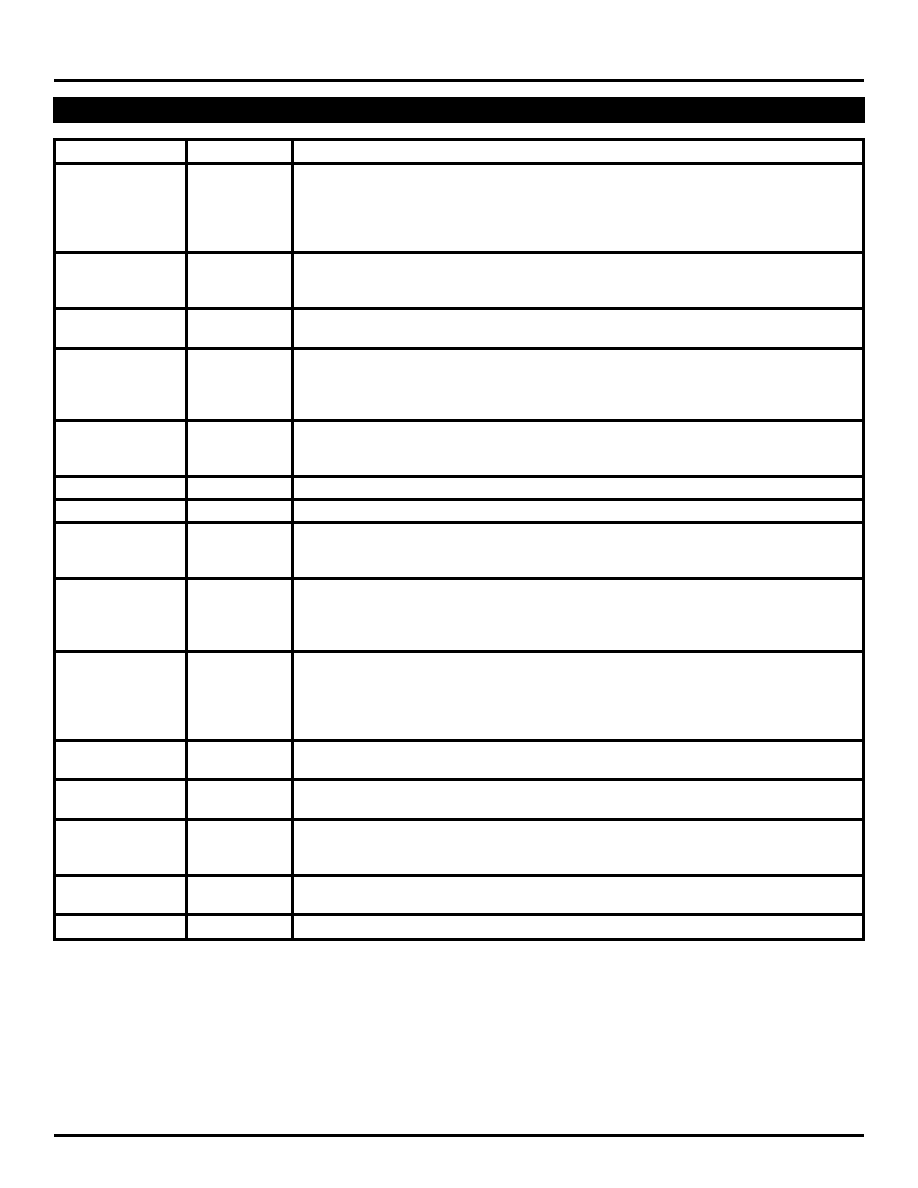

Pin Number

Pin Name

Pin Function

23, 25, 26, 27, 29,

D[0:9]

CMOS, ECL, or TTL Select Inputs: These digital control signals adjust the amount of

30, 31, 32, 1, 2

delay from IN to Q. Please refer to the delay selection Table 1 for delay values. Figure 9

shows how to interface these inputs to various logic family standards. These inputs default

to logic low when left unconnected. Bit 0 is the least significant bit, and bit 9 is the most

significant bit.

3

D[10]

CMOS, ECL, or TTL Select Input: This input latches just like D[0:9] does. It drives the

CASCADE, /CASCADE differential pair. Use only when cascading two or more

SY100EP196V to extend the range of delays required.

4, 5

IN, /IN

ECL Input: This is the signal to be delayed. If this input pair is left unconnected, this is

equivalent to a logic low input.

6

VBB

Voltage Output Reference: When using a single-ended logic source for IN and /IN,

connect the unused input of the differential pair to this pin. This pin can also re-bias AC–

coupled inputs to IN and /IN. When used, de-couple this pin to V

CC through an 0.01F

capacitor. Limit current sinking or sourcing to 0.5mA or less.

7

VEF

Voltage Output: Connect this pin to VCF when the D inputs are ECL. Refer to the digital

control logic standard section of the Functional Description to interface the D inputs to

CMOS or TTL.

8

VCF

Voltage Input: The voltage at this pin sets the logic transition threshold for the D inputs.

9, 24, 28

VEE

Most negative supply. Supply ground for PECL systems.

10

LEN

ECL Control Input: When logic low, the D inputs flow through. Any changes to the D inputs

reflect in the delay between IN, /IN and Q, /Q. When logic high, the logic values at D are

latched, and these latched bits determine the delay.

11

SETMIN

ECL Control Input: When logic high, the contents of the D register are reset. This sets the

delay to the minimum possible, equivalent to D[0:9] being set to 0000000000. When logic

low, the value of the D register, or the logic value of SETMAX determines the delay from

IN, /IN to Q, /Q. This input defaults to logic low when left unconnected.

12

SETMAX

ECL Control Input: When logic high and SETMIN is logic low, the contents of the D

register are set high, and the delay is set to one step greater than the maximum possible

with D[0:9] set to 1111111111. When logic low, the value of the D register, or the logic

value of SETMIN determines the delay from IN, /IN to Q, /Q. This input defaults to logic

low when left unconnected.

13, 18, 19, 22

VCC

Most positive supply: Supply ground for NECL systems. Bypass to V

EE with 0.1F and

0.01

F low ESR capacitors.

14, 15

CASCADE,

ECL Outputs: These outputs are used when cascading two or more SY100EP196V to

/CASCADE

extend the delay range required.

16

/EN

ECL Control Input: When set active low, Q, /Q are a delayed version of IN, /IN. When set

inactive high, IN, /IN are gated such that Q, /Q become a differential logic low. This input

defaults to logic low when left unconnected.

17

FTUNE

Voltage Control Input: By varying the voltage at this pin from V

CC through VEE, the delay

may be fine tuned in about a 30ps range. Please refer to Figure 13.

20, 21

Q, /Q

ECL Outputs: This signal pair is the delayed version of IN, /IN.

PIN DESCRIPTION

相关PDF资料 |

PDF描述 |

|---|---|

| SY100EP196VTC | ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 |

| SY100S336AJC | 100S SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, PQCC28 |

| SY100S336AFC | 100S SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CQFP24 |

| SY100S336DC | 100S SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDIP24 |

| SY54017ARMGTR | 54017 SERIES, 2 LINE TO 1 LINE MULTIPLEXER, COMPLEMENTARY OUTPUT, QCC16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY100EP196VTG | 功能描述:延迟线/计时元素 3.3V/5V 2.5 GHz Programmable Delay Line w/Fine Tune (I Temp, Green) RoHS:否 制造商:Micrel 功能:Active Programmable Delay Line 传播延迟时间:1000 ps 工作温度范围: 封装 / 箱体:QFN-24 封装:Tube |

| SY100EP196VTG TR | 功能描述:延迟线/计时元素 3.3V/5V 2.5 GHz Programmable Delay Line w/Fine Tune (I Temp, Green) RoHS:否 制造商:Micrel 功能:Active Programmable Delay Line 传播延迟时间:1000 ps 工作温度范围: 封装 / 箱体:QFN-24 封装:Tube |

| SY100EP196VTI | 功能描述:IC DELAY LINE 1024TAP 32-TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:100EP, ECL Pro® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR) |

| SY100EP196VTI TR | 功能描述:IC DELAY LINE 1024TAP 32-TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:100EP, ECL Pro® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR) |

| SY100EP210UTG | 功能描述:缓冲器和线路驱动器 2.5-5V Dual 1:5 PECL Fanout Buffer (I Temp, Green) RoHS:否 制造商:Micrel 输入线路数量:1 输出线路数量:2 极性:Non-Inverting 电源电压-最大:+/- 5.5 V 电源电压-最小:+/- 2.37 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。