参数资料

| 型号: | SY100EP196VTG |

| 厂商: | Micrel Inc |

| 文件页数: | 5/18页 |

| 文件大小: | 0K |

| 描述: | IC DELAY LINE 1024TAP 32-TQFP |

| 标准包装: | 250 |

| 系列: | 100EP, ECL Pro® |

| 标片/步级数: | 1024 |

| 功能: | 可编程 |

| 延迟到第一抽头: | 2.05ns |

| 接头增量: | 10ps |

| 可用的总延迟: | 2.05ns ~ 12.2ns |

| 独立延迟数: | 1 |

| 电源电压: | 3 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP |

| 供应商设备封装: | 32-TQFP |

| 包装: | 托盘 |

| 产品目录页面: | 1088 (CN2011-ZH PDF) |

| 其它名称: | 576-2462 SY100EP196VTG-ND |

13

ECL Pro

SY100EP196V

Micrel, Inc.

M9999-072706

hbwhelp@micrel.com or (408) 955-1690

FUNCTIONAL DESCRIPTION

SY100EP196V is a programmable delay line, varying the

delay of a PECL or NECL input signal by any amount between

about 2.2ns and 12.2ns. A 10-bit digital control register affords

delay steps of approximately 10ps.

SY100EP196V implements the delay using a multiplexer

chain and a set of fixed delay elements. Under digital control,

various subsets of the delay elements are included in the

signal chain. To simplify interfacing, the 10-bit digital delay

control word interfaces to PECL, CMOS, or TTL interface

standards.

Since multiplexers must appear in the delay path,

SY100EP196V has a minimum delay of about 2.2ns. Delays

below this value are not possible. In addition, when cascading

multiple SY100EP196V to extend the delay range, the

minimum delay is about 2.2ns times the number of

SY100EP196V in cascade. An eleventh control bit, D[10],

along with the CASCADE and /CASCADE outputs and the

SETMIN and SETMAX inputs, simplifies the task of cascading.

Signal Path Logic Standard

The signal path, from IN, /IN to Q, /Q, interfaces to PECL,

LVPECL, or NECL signals, as shown in Table 6. The choice

of signal path logic standard may limit possible choices for

the delay control inputs, D.

Input Enable

The /EN input gates the signal at IN, /IN. When disabled,

the input is effectively gated out, just as if a logic low was

being provided to SY100EP196V.

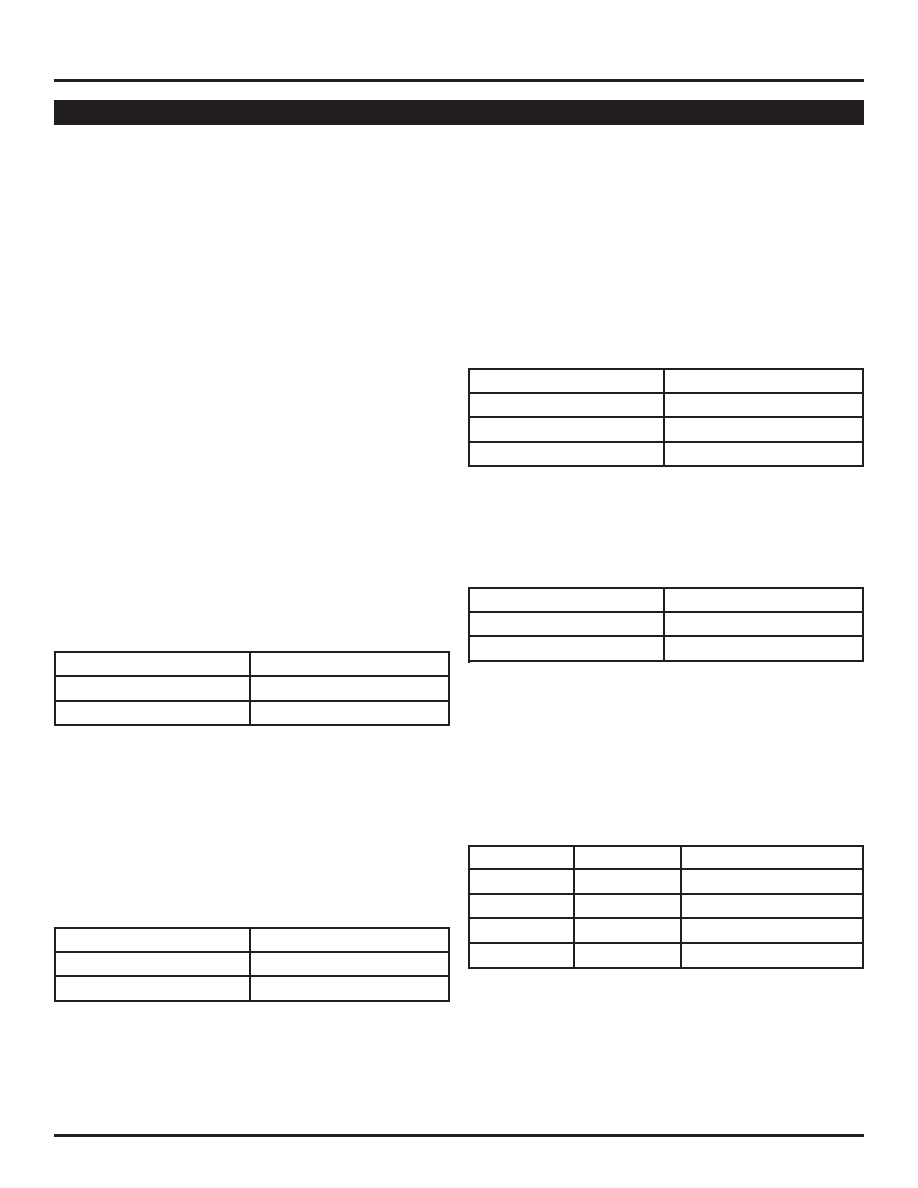

/EN

Value at Q, /Q

L

IN, /IN Delayed

H

Logic Low Delayed

Table 1. /EN Truth Table

Digital Control Latch

SY100EP196V can capture the digital delay control word

into its internal 11-bit latch, 10 bits for D[0:9], and an extra bit

for the D[10] cascade control. The LEN input controls the

action of this latch, as per Table 2.

Note that the LEN input is always PECL, LVPECL, or

NECL, the same as the IN, /IN signal pair. The 11-bit delay

control word, however, may also be CMOS or TTL.

LEN

Latch Action

L

Pass Through D[0:10]

H

Latch D[0:10]

Table 2. LEN Truth Table

The nominal delay value is based on the binary value in

D[0:9], where D[0] is the least significant bit, and D[9] is the

most significant bit. This delay from IN, /IN to Q, /Q is about:

t

2200 10

value D 9:0 + delay FTUNE ,ps

=+

×

[]

()

Digital Control Logic Standard

When used in systems where VEE connects to ground,

SY100EP196V may interface either to PECL, CMOS, or TTL

on its D[0:10] inputs. To this end, the VCF pin sets the

threshold at which the D inputs switch between logic low and

logic high.

As shown in Table 3, connecting VCF to VEF sets the

threshold to PECL (if VCC is 5V) or LVPECL (if VCC is 3.3V).

Leaving VCF and VEF open yields a threshold suitable for

detecting CMOS output logic levels. Leaving VEF open and

connecting VCF to a 1.5V source allows the D inputs to accept

TTL signals.

Logic Standard

VCF Connects To

ECL, PECL

VEF

CMOS

No Connect

TTL

1.5V Source

Table 3. Digital Control Standard Truth Table

If a 1.5V source is not available, connecting VCF to VEE

through an appropriate resistor will bias VCF at about 1.5V.

The value of this resistor depends on the VCC supply, as

indicated in Table 4.

VCC

Resistor Value

3.3V

1.5k

5.0V

500

Table 4. Resistor Values for TTL Input

Cascade Logic

SY100EP196V is designed to ease cascading multiple

devices in order to achieve a greater delay range. The SETMIN

and SETMAX pins accomplish this, as set out in the

applications section below. SETMIN and SETMAX override

the delay by changing the value in the D latch register. Table

5 lists the action of these pins.

SETMIN

SETMAX

Nominal Delay (ps)

LL

As per D Latch

LH

2200 + 10 × 1024

HL

2200

HH

Not Allowed

Table 5. SETMIN and SETMAX Action

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B40-MY-F1 | CONVERTER MOD DC/DC 5V 50W |

| LTC6994CDCB-2#TRMPBF | IC DELAY LINE 6-DFN |

| AD5274BRMZ-20-RL7 | IC DGTL POT 20K 256POS 10MSOP |

| AD5170BRMZ2.5-RL7 | IC DGTL POT 256POS 2.5K 10MSOP |

| MS27499E16F55SA | CONN RCPT 55POS BOX MNT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY100EP196VTG TR | 功能描述:延迟线/计时元素 3.3V/5V 2.5 GHz Programmable Delay Line w/Fine Tune (I Temp, Green) RoHS:否 制造商:Micrel 功能:Active Programmable Delay Line 传播延迟时间:1000 ps 工作温度范围: 封装 / 箱体:QFN-24 封装:Tube |

| SY100EP196VTI | 功能描述:IC DELAY LINE 1024TAP 32-TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:100EP, ECL Pro® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR) |

| SY100EP196VTI TR | 功能描述:IC DELAY LINE 1024TAP 32-TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:100EP, ECL Pro® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR) |

| SY100EP210UTG | 功能描述:缓冲器和线路驱动器 2.5-5V Dual 1:5 PECL Fanout Buffer (I Temp, Green) RoHS:否 制造商:Micrel 输入线路数量:1 输出线路数量:2 极性:Non-Inverting 电源电压-最大:+/- 5.5 V 电源电压-最小:+/- 2.37 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Reel |

| SY100EP210UTG TR | 功能描述:缓冲器和线路驱动器 2.5-5V Dual 1:5 PECL Fanout Buffer (I Temp, Green) RoHS:否 制造商:Micrel 输入线路数量:1 输出线路数量:2 极性:Non-Inverting 电源电压-最大:+/- 5.5 V 电源电压-最小:+/- 2.37 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。