参数资料

| 型号: | SY10E336JZ |

| 厂商: | Micrel Inc |

| 文件页数: | 1/4页 |

| 文件大小: | 0K |

| 描述: | IC TXRX BUS 3BIT REG 28-PLCC |

| 标准包装: | 38 |

| 系列: | 10E |

| 逻辑类型: | 收发器,非反相 |

| 元件数: | 1 |

| 每个元件的位元数: | 3 |

| 电源电压: | 4.2 V ~ 5.5 V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC |

| 包装: | 管件 |

1

SY10E336

SY100E336

Micrel, Inc.

M9999-032206

hbwhelp@micrel.com or (408) 955-1690

FEATURES

s 25

cutoff bus output

s Extended 100E VEE range of –4.2V to –5.5V

s 50

receiver output

s Transmit and receive registers

s 1500ps max. clock to bus

s 1000ps max. clock to Q

s Internal edge slow-down capacitors on bus outputs

s Additional package ground pins

s Fully compatible with industry standard 10KH,

100K ECL levels

s Internal 75K

input pulldown resistors

s Fully compatible with Motorola MC10E/100E336

s Available in 28-pin PLCC package

DESCRIPTION

The SY10/100E336 offer three bus transceivers with

both transmit and receive registers and are designed for

use in new, high-performance ECL systems. The bus

outputs (BUS0 - BUS2) are designed to drive a 25

bus.

The receive outputs (Q0 – Q2) are specified for 50

. The

bus outputs feature a normal logic HIGH level (VOH) and a

cutoff LOW level when at a logic LOW. At cutoff, the outputs

go to –2.0V and the output emitter-follower is “off”,

presenting a high impedance to the bus. The bus outputs

have edge slow-down capacitors.

The Transmit Enable pins (TEN) determine whether

current data is held in the transmit register or new data is

loaded from the A/B inputs. A logic LOW on both of the bus

enable inputs (BUSEN), when clocked through the register,

disables the bus outputs to –2.0V.

The receiver section clocks bus data into the receive

registers after gating with the Receive Enable (RXEN)

input.

All registers are clocked by rising edge of CLK1 or CLK2

(or both).

Additional grounding is provided through the ground

pins (GND) which should be connected to 0V. The GND

pins are not electrically connected to the chip.

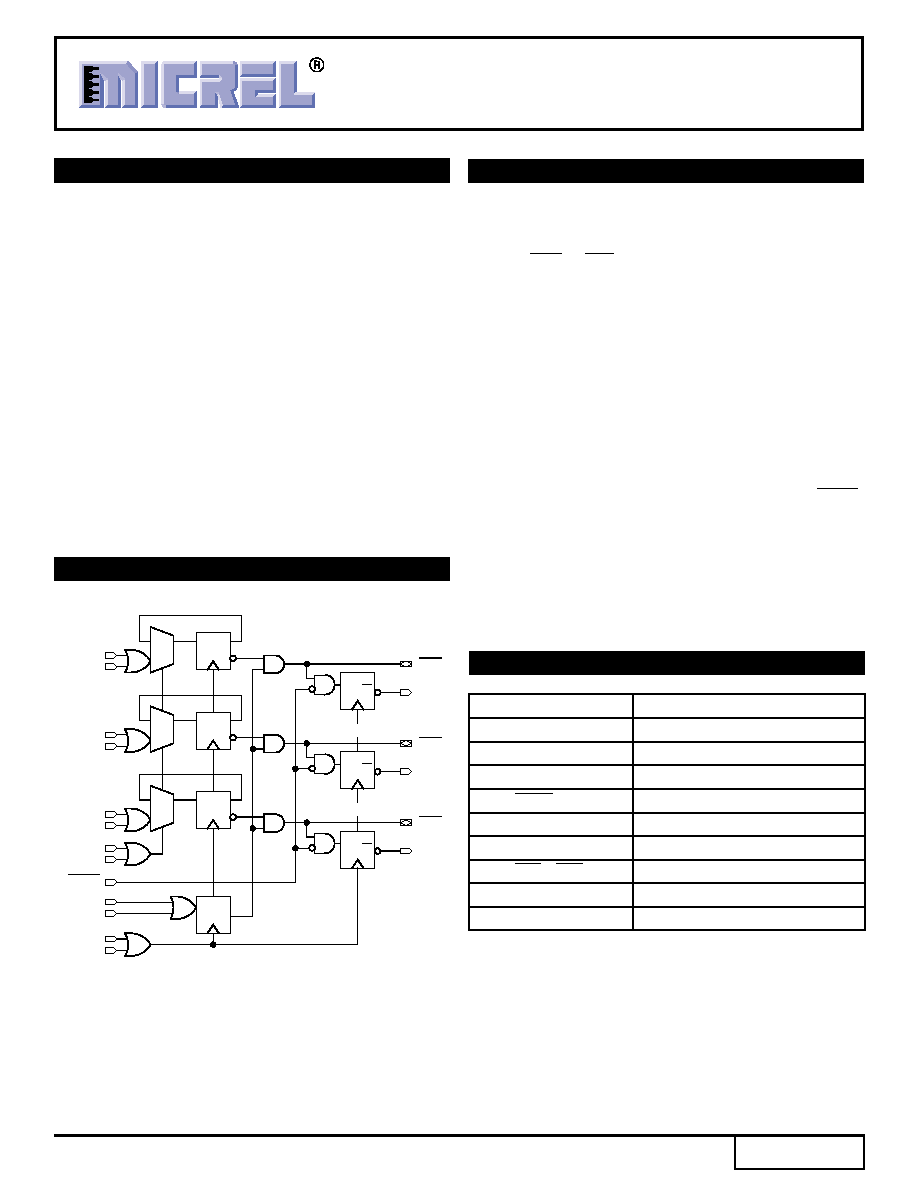

3-BIT REGISTERED

BUS TRANSCEIVER

Pin

Function

A0–A2

Data Inputs A

B0–B2

Data Inputs B

TEN1, 2

Transmit Enable Inputs

RXEN

Receive Enable Input

BUSEN1, 2

Bus Enable Inputs

CLK1, 2

Clock Inputs

BUS0–BUS2

25

Cutoff Bus Outputs

Q0–Q2

Receive Data Outputs

VCCO

VCC to Output

PIN NAMES

SY10E336

SY100E336

Rev.: G

Amendment: /0

Issue Date:

March 2006

BLOCK DIAGRAM

0

1

DQ

D

Q

50

25

CUTOFF

0

1

DQ

D

Q

50

25

CUTOFF

0

1

DQ

D

Q

50

25

CUTOFF

Q0

BUS0

Q1

BUS1

Q2

BUS2

D

Q

A0

B0

A1

B1

A2

B2

TEN1

TEN2

BUSEN1

BUSEN2

CLK1

CLK2

RXEN

相关PDF资料 |

PDF描述 |

|---|---|

| SY100E337JZ TR | IC TXRX BUS 3BIT SCAM REG 28PLCC |

| OSTTS21A15B | TERM BLOCK PLUG 7.5MM 21POS |

| N74F243D,602 | IC BUS TRANSCVR 3-ST 4BIT 14SOIC |

| OSTTS21A15A | TERM BLOCK PLUG 7.5MM 21POS |

| OSTHI163051 | CONN PLUG HEADER 16PS 7.62MM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY10E336JZ TR | 功能描述:IC TXRX BUS 3BIT REG 28-PLCC RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:10E 标准包装:1,000 系列:74ABT 逻辑类型:寄存收发器,非反相 元件数:1 每个元件的位元数:8 输出电流高,低:32mA,64mA 电源电压:4.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) |

| SY10E337JC | 功能描述:IC TXRX BUS 3BIT SCAM REG 28PLCC RoHS:否 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:10E 标准包装:1,000 系列:74ABT 逻辑类型:寄存收发器,非反相 元件数:1 每个元件的位元数:8 输出电流高,低:32mA,64mA 电源电压:4.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) |

| SY10E337JZ | 功能描述:IC TXRX BUS 3BIT SCAM REG 28PLCC RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:10E 标准包装:1,000 系列:74ABT 逻辑类型:寄存收发器,非反相 元件数:1 每个元件的位元数:8 输出电流高,低:32mA,64mA 电源电压:4.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) |

| SY10E337JZ TR | 功能描述:IC TXRX BUS 3BIT SCAM REG 28PLCC RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:10E 标准包装:1,000 系列:74ABT 逻辑类型:寄存收发器,非反相 元件数:1 每个元件的位元数:8 输出电流高,低:32mA,64mA 电源电压:4.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) |

| SY10E404JC | 功能描述:IC GATE AND/NAND QUAD 28-PLCC RoHS:否 类别:集成电路 (IC) >> 逻辑 - 栅极和逆变器 - 多功能,可配置 系列:10E 产品变化通告:Product Obsolescence 05/Oct/2010 标准包装:100 系列:- 逻辑类型:可配置多功能 电路数:2 输入数:2 施密特触发器输入:无 输出类型:差分 输出电流高,低:- 电源电压:2.375 V ~ 3.465 V 工作温度:-40°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-LBGA,FCBGA 供应商设备封装:16-FCBGA(4x4) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。