参数资料

| 型号: | SY55851AUKG TR |

| 厂商: | Micrel Inc |

| 文件页数: | 8/8页 |

| 文件大小: | 0K |

| 描述: | IC GATE UNIV 3GHZ 50 OHM 10-MSOP |

| 标准包装: | 1,000 |

| 系列: | SY55 |

| 逻辑类型: | 可配置多功能 |

| 电路数: | 1 |

| 输入数: | 2 |

| 施密特触发器输入: | 无 |

| 输出类型: | 差分 |

| 电源电压: | 2.3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-TFSOP,10-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 10-MSOP |

| 包装: | 带卷 (TR) |

| 其它名称: | SY55851AUKGTR SY55851AUKGTR-ND |

8

Precision Edge

SY58012U

Micrel, Inc.

M9999-051408

hbwhelp@micrel.com or (408) 955-1690

k

n

i

L

t

e

h

S

a

t

a

D

n

o

it

c

n

u

F

r

e

b

m

u

N

t

r

a

P

SY58011U

7GHz, 1:2 CML Fanout Buffer/Translator

http://www.micrel.com/product-info/products/sy58011u.shtml

With Internal Input Termnations

SY58012U

5GHz, 1:2 LVPECL Fanout Buffer/Translator

http://www.micrel.com/product-info/products/sy58012u.shtml

With Internal Input Termination

SY58013U

6GHz, 1:2 Fanout Buffer/Translator w/400mV

http://www.micrel.com/product-info/products/sy58013u.shtml

LVPECL Outputs and Internal Terminations

l

m

t

h

s

.

s

n

o

it

u

l

o

s

/

s

a

/

o

f

n

i-

t

c

u

d

o

r

p

/

m

o

c

.l

e

r

c

i

m

.

w

//

:

p

tt

h

s

n

o

it

u

l

o

S

W

B

H

7

1

3

0

-

M

RELATED MICREL PRODUCTS AND SUPPORT DOCUMENTATION

R2

82

R2

82

ZO = 50

+3.3V*

VT = VCC —2V

R1

130

R1

130

+3.3V*

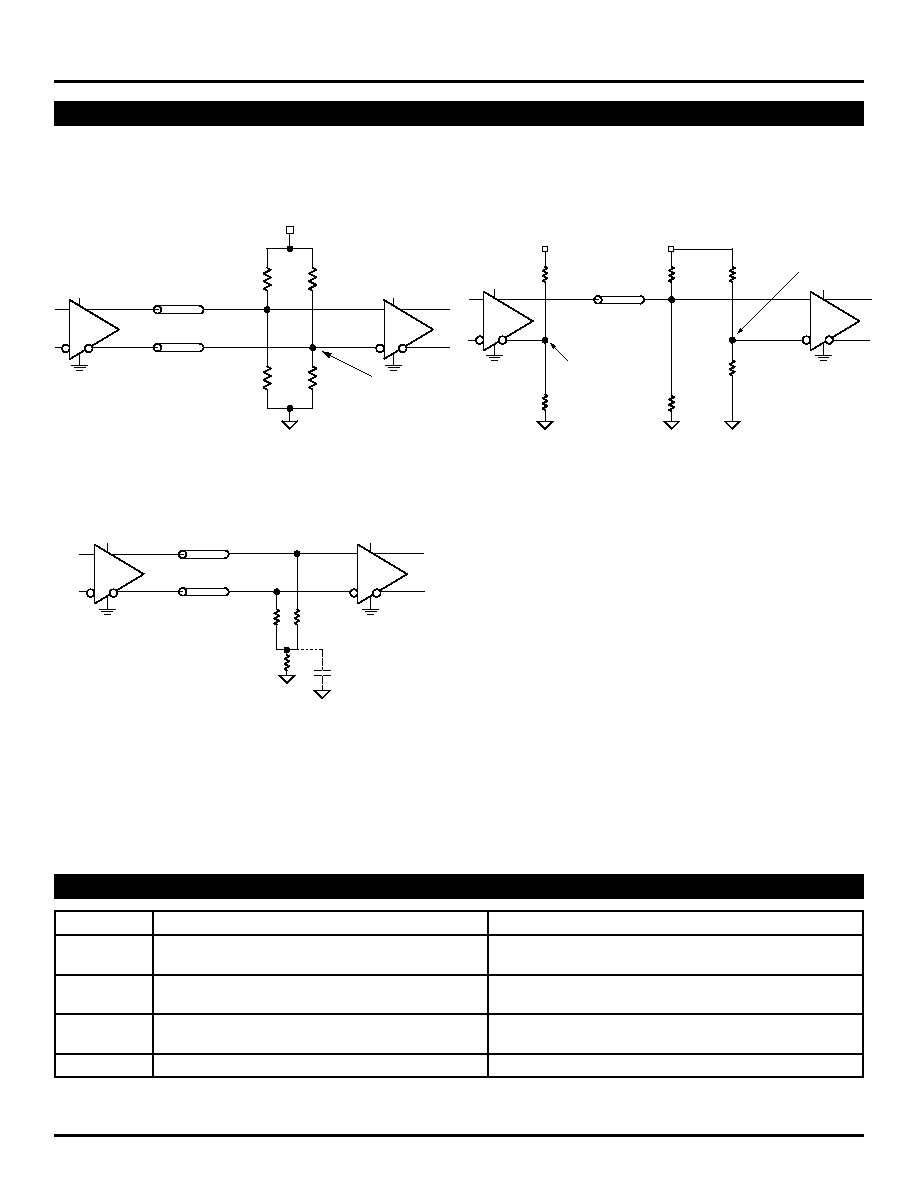

Figure 5. Parallel Termination-Thevenin Equivalent

Note 1. For +2.5V systems: R1 = 250, R2 = 62.5

Note 2. For +3.3V systems: R1 = 130, R2 = 82

Z = 50

50

V

3

.

3

+

V

3

.

3

+

n

o

it

a

n

it

s

e

d

e

c

r

u

o

s

Rb C1

0.01F

(optional)

Figure 6. Three-Resistor “Y–Termination”

Note 1. Power-saving alternative to Thevenin termination.

Note 2. Placeterminationresistorsasclosetodestinationinputsaspossible.

Note 3. Rb resistor sets the DC bias voltage, equal to VT.

For +2.5V systems Rb = 19.

For +3.3V systems Rb = 46 to 50.

Note 4. C1 is an optional bypass capacitor intended to compensate for any

tr/tf mismatches.

LVPECL OUTPUT

+3.3V

ZO = 50

R2

82

+3.3V

R1

130

R1

130

R2

82

VT = VCC —2V

Q

/Q

R4

1k

R3

1.6k

VT = VCC —1.3V

Figure 7. Terminating Unused I/O

Note 1. Unused output (/Q) must be terminated to balance the output.

Note 2. For +2.5V systems: R1 = 250, R2 = 62.5, R3 = 1.25k,

R4 = 1.2k.

For +3.3V systems: R1 = 130, R2 = 82, R3 = 1k, R4 = 1.6k.

Note 3. Unused output pairs (Q and /Q) may be left floating.

LVPECL output have very low output impedance (open

emitter), and small signal swing which results in low EMI.

LVPECL is ideal for driving 50 and 100 controlled

impedance transmission lines. There are several techniques

in terminating the LVPECL output, as shown in Figures 5

through 7.

相关PDF资料 |

PDF描述 |

|---|---|

| TXR21AB00-1410AI | ADPTR TINEL LOCK STR SHELL 14 |

| SY10E104JY TR | IC GATE AND/NAND QUINT 28-PLCC |

| SY10E101JY TR | IC GATE OR/NOR QUAD 4INP 28-PLCC |

| TXR18AB00A1206AI | ADPTR TINEL LOCK STR SHELL 12 |

| TXR41AB00-1810AI | ADPTR TINEL LOCK STR SHELL 18,19 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY55851AUKI | 功能描述:IC GATE UNIV 3GHZ 50 OHM 10MSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 栅极和逆变器 - 多功能,可配置 系列:SY55 产品变化通告:Product Obsolescence 05/Oct/2010 标准包装:100 系列:- 逻辑类型:可配置多功能 电路数:2 输入数:2 施密特触发器输入:无 输出类型:差分 输出电流高,低:- 电源电压:2.375 V ~ 3.465 V 工作温度:-40°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-LBGA,FCBGA 供应商设备封装:16-FCBGA(4x4) 包装:带卷 (TR) |

| SY55851AUKI TR | 功能描述:IC GATE 3.0GHZ 50OHM 10-MSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 栅极和逆变器 - 多功能,可配置 系列:SY55 产品变化通告:Product Obsolescence 05/Oct/2010 标准包装:100 系列:- 逻辑类型:可配置多功能 电路数:2 输入数:2 施密特触发器输入:无 输出类型:差分 输出电流高,低:- 电源电压:2.375 V ~ 3.465 V 工作温度:-40°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-LBGA,FCBGA 供应商设备封装:16-FCBGA(4x4) 包装:带卷 (TR) |

| SY55851AUKITR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:2.5V/3V, 3.0GHz CML AnyGate?ANY LOGIC WITH 50Ω or 100Ω OUTPUTS |

| SY55851UKC | 功能描述:IC GATE 3.0GHZ 100OHM 10-MSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 栅极和逆变器 - 多功能,可配置 系列:SY55 产品变化通告:Product Obsolescence 05/Oct/2010 标准包装:100 系列:- 逻辑类型:可配置多功能 电路数:2 输入数:2 施密特触发器输入:无 输出类型:差分 输出电流高,低:- 电源电压:2.375 V ~ 3.465 V 工作温度:-40°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-LBGA,FCBGA 供应商设备封装:16-FCBGA(4x4) 包装:带卷 (TR) |

| SY55851UKC TR | 功能描述:IC GATE 3.0GHZ 100OHM 10-MSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 栅极和逆变器 - 多功能,可配置 系列:SY55 产品变化通告:Product Obsolescence 05/Oct/2010 标准包装:100 系列:- 逻辑类型:可配置多功能 电路数:2 输入数:2 施密特触发器输入:无 输出类型:差分 输出电流高,低:- 电源电压:2.375 V ~ 3.465 V 工作温度:-40°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-LBGA,FCBGA 供应商设备封装:16-FCBGA(4x4) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。