参数资料

| 型号: | SY89202UMI |

| 厂商: | Micrel Inc |

| 文件页数: | 4/6页 |

| 文件大小: | 0K |

| 描述: | IC CLK BUFF DVDR MUX 1:8 32-MLF |

| 标准包装: | 60 |

| 系列: | Precision Edge® |

| 类型: | 扇出缓冲器(分配),除法器,多路复用器 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:8 |

| 差分 - 输入:输出: | 是/是 |

| 输入: | CML,LVDS,PECL |

| 输出: | LVPECL |

| 频率 - 最大: | 1.5GHz |

| 电源电压: | 2.375 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,32-MLF? |

| 供应商设备封装: | 32-MLF?(5x5) |

| 包装: | 管件 |

Micrel, Inc.

SY89202U

August 2007

4

M9999-083107-C

hbwhelp@micrel.com or (408) 955-1690

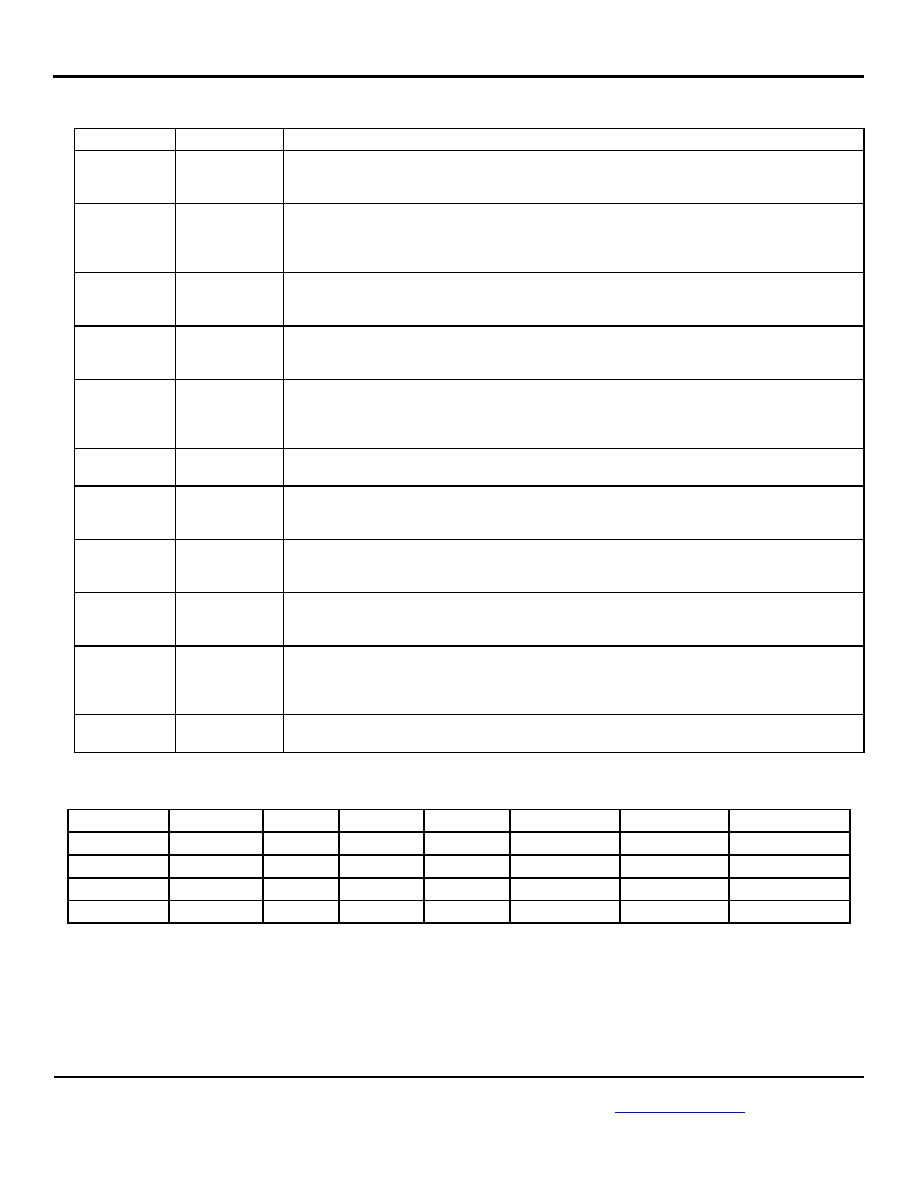

Pin Description

Pin Number

Pin Name

Pin Function

2, 7, 8

DIVSEL1

DIVSEL2

DIVSEL3

Single-Ended Inputs: These TTL/CMOS inputs select the divide ratio for each of the three

banks of outputs. Note that each of these inputs is internally connected to a 25k

pull-up

resistor and will default to logic HIGH state if left open. The input-switching threshold is VCC/2.

3, 6

IN, /IN

Differential Input: This input pair is the differential signal input to the device. This input accepts

AC- or DC-coupled signals as small as 100mV. The input pair internally terminates to a VT pin

through 50

. Note that these inputs will default to an indeterminate state if left open. Please

refer to the “Input Interface Applications” section for more details.

4

VT

Input Termination Center-Tap: Each side of the differential input pair terminates to the VT pin.

The VT pin provides a center-tap to a termination network for maximum interface flexibility.

See “Input Interface Applications” section for more details.

5

VREF-AC

Reference Voltage: This output biases to VCC –1.2V. It is used for AC-coupling inputs IN and

/IN. For AC-coupled applications, connect VREF-AC directly to the VT pin. Bypass with 0.01F

low ESR capacitor to VCC.

9

EN

Single-Ended Input: This TTL/CMOS input disables and enables the Q0 – Q7 outputs. This

input is internally connected to a 25k

pull-up resistor and will default to logic HIGH state if left

open. The input-switching threshold is VCC/2. For the input enable and disable functional

description, refer to “Timing Diagram” section.

10, 19, 22, 31

VCC

Positive power supply. Bypass with 0.1F||0.01F low ESR capacitors as close to VCC pins

as possible.

16, 15, 14,

13, 12, 11

Q4, /Q4, Q5,

/Q5, Q6, /Q6

Bank 2 LVPECL differential output pairs controlled by DIVSEL2: LOW, Q4 – Q6 = ÷2, HIGH,

Q4 – Q6 = ÷4. Unused output pairs may be left open. Each output is designed to drive 800mV

into 50

terminated at VCC–2V.

30, 29, 28,

27, 26, 25,

24, 23

Q0, /Q0, Q1,

/Q1, Q2, /Q2,

Q3, /Q3

Bank 1 LVPECL differential output pairs controlled by DIVSEL1: LOW, Q0 – Q3 = ÷1, HIGH,

Q0 – Q3 = ÷2. Unused output pairs may be left open. Each output is designed to drive 800mV

into 50

terminated at VCC–2V.

18, 17

Q7, /Q7

Bank 3 LVPECL differential output pair controlled by DIVSEL3: LOW, Q7 = ÷2, HIGH, Q7 =

÷4. Unused output pairs may be left open. Each output is designed to drive 800mV into 50

terminated at VCC–2V.

32

/MR

Single-Ended Input: This TTL/CMOS-compatible master reset function asynchronously sets

Q0 – Q7 outputs LOW and /Q0 – /Q7 outputs HIGH, and holds them in that state as long as

the /MR input remains LOW. This input is internally connected to a 25k

pull-up resistor and

will default to a logic HIGH state if left open. The input-switching threshold is VCC/2.

1, 20, 21

GND,

Exposed Pad

Ground: Ground pin and exposed pad must be connected to the same ground plane.

Truth Table

/MR

( 1)

EN

( 2, 3)

DIVSEL1

DIVSEL2

DIVSEL3

Q0 – Q3

Q4 – Q6

Q7

0

X

0

1

0

X

0

1

0

1

2

1

2

4

Notes:

1. /MR asynchronously forces Q0 – Q7 LOW (/Q0 - /Q7 HIGH).

2. EN forces Q0 – Q7 LOW between 2 and 6 input clock cycles after the falling edge of EN. Refer to “Timing Diagram” section.

3. EN synchronously enables the outputs between 2 and 6 input clock cycles after the rising edge of EN. Refer to “Timing Diagram” section.

相关PDF资料 |

PDF描述 |

|---|---|

| V300A12H500BG2 | CONVERTER MOD DC/DC 12V 500W |

| SY58012UMI | IC CLK BUFFER TRANSLA 1:2 16-MLF |

| V300A12H500BF3 | CONVERTER MOD DC/DC 12V 500W |

| AD5322BRM-REEL7 | IC DAC 12BIT DUAL W/BUFF 10-MSOP |

| V300A12H500B | CONVERTER MOD DC/DC 12V 500W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY89202UMI TR | 功能描述:IC CLK BUFF DVDR MUX 1:8 32-MLF RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:Precision Edge® 标准包装:1 系列:HiPerClockS™ 类型:扇出缓冲器(分配),多路复用器 电路数:1 比率 - 输入:输出:2:18 差分 - 输入:输出:是/无 输入:CML,LVCMOS,LVPECL,LVTTL,SSTL 输出:LVCMOS,LVTTL 频率 - 最大:250MHz 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:- 其它名称:800-1923-6 |

| SY89206V | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3.3V/5V 1GHz PECL/ECL Differential Receiver/Buffer |

| SY89206V-EVAL | 功能描述:EVAL BOARD FOR SY89206VMG RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:Precision Edge® 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| SY89206VMG TR | 功能描述:缓冲器和线路驱动器 3.3V/5V 1GHz, Ultrasmall Differential Receiver/Buffer (I Temp, Green) RoHS:否 制造商:Micrel 输入线路数量:1 输出线路数量:2 极性:Non-Inverting 电源电压-最大:+/- 5.5 V 电源电压-最小:+/- 2.37 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Reel |

| SY89206VMGTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V/5V 1GHz DIFFERENTIAL PECL/ECL RECEIVER/BUFFER |

发布紧急采购,3分钟左右您将得到回复。