- 您现在的位置:买卖IC网 > PDF目录98150 > SY89827LHG (MICREL INC) 89827 SERIES, LOW SKEW CLOCK DRIVER, 20 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP64 PDF资料下载

参数资料

| 型号: | SY89827LHG |

| 厂商: | MICREL INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 89827 SERIES, LOW SKEW CLOCK DRIVER, 20 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP64 |

| 封装: | LEAD FREE, TQFP-64 |

| 文件页数: | 6/11页 |

| 文件大小: | 747K |

| 代理商: | SY89827LHG |

4

Precision Edge

SY89827L

Micrel, Inc.

M9999-061306

hbwhelp@micrel.com or (408) 955-1690

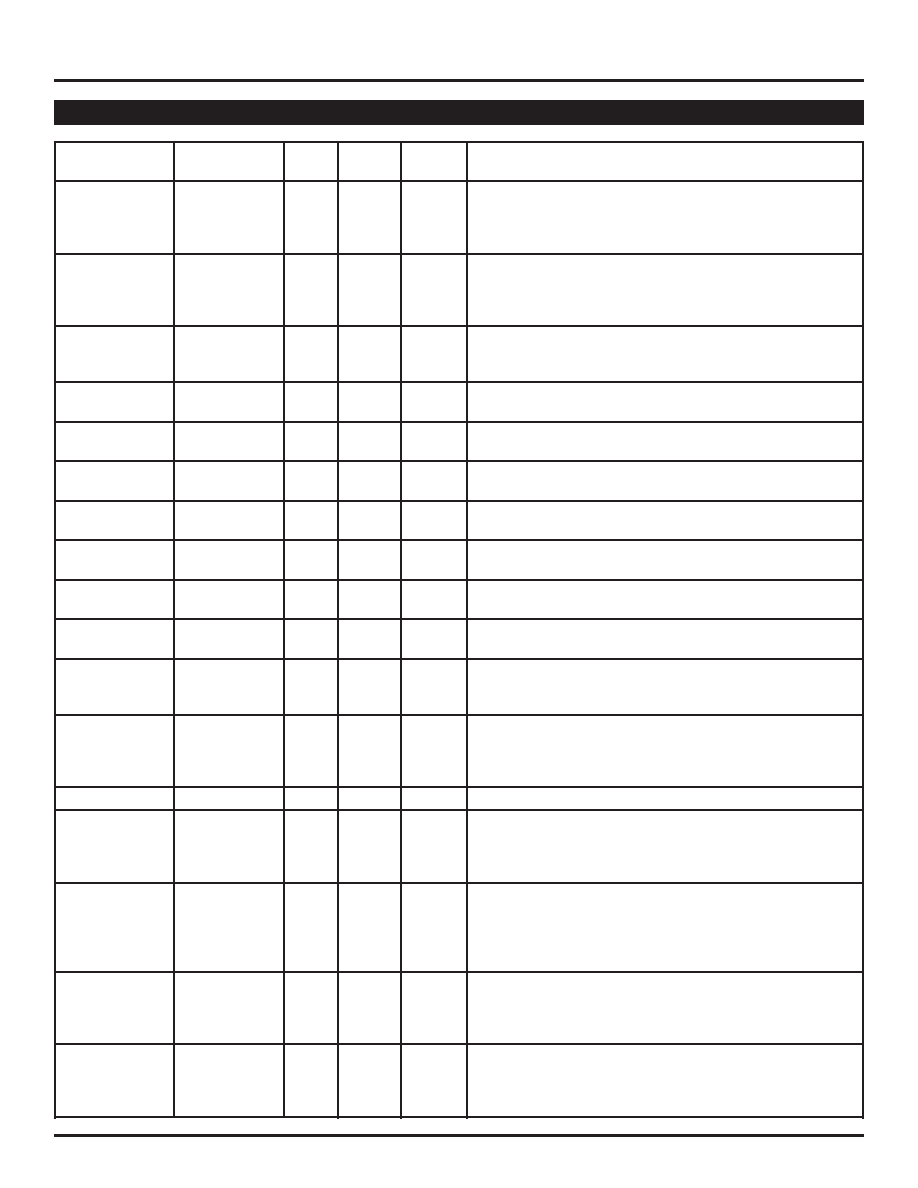

PIN DESCRIPTIONS

Internal

Pin Number

Pin Name

I/O

Type

P/U

Pin Function

5, 6

HSTL_CLKA

Input

HSTL

Differential clock input selected by CLK_SEL1, SEL1 and SEL2.

/HSTL_CLKA

Can be left floating if not selected. Floating input, if selected

produces an indeterminate output. HSTL input signal requires

external termination 50-to-GND.

2, 3

HSTL_CLKB

Input

HSTL

Differential clock input selected by CLK_SEL1, SEL1 and SEL2.

/HSTL_CLKB

Can be left floating if not selected. Floating input, if selected

produces an indeterminate output. HSTL input signal requires

external termination 50-to-GND.

8, 9

LVPECL_CLKA

Input

LVPECL

75k

Differential clock input selected by CLK_SEL1, SEL1 and SEL2.

/LVPECL_CLKA

pull-down

Can be left floating. Floating input, if selected produces a LOW

at output. Requires external termination. See Figure 1.

12, 13

LVPECL_CLKB

Input

LVPECL

75k

Differential clock input selected by CLK_SEL2, SEL1 and SEL2.

/LVPECL_CLKB

pull-down

Requires external termination. See Figure 1.

7

CLK_SEL1

Input

LVTTL/

11k

Selects HSTL_CLKA input when LOW and LVPECL_CLKA

CMOS

Pull-up

input when HIGH.

14

CLK_SEL2

Input

LVTTL/

11k

Selects HSTL_CLKB input when LOW and LVPECL_CLKB

CMOS

Pull-up

input when HIGH.

16

SEL1

Input

LVTTL/

11k

Selects input source CLKA when LOW and CLKB

CMOS

Pull-up

when HIGH for outputs Q0 – Q9 and /Q0 – /Q9.

1

SEL2

Input

LVTTL/

11k

Selects input source CLKA when LOW and CLKB

CMOS

Pull-up

when HIGH for outputs Q10 – Q19 and /Q10 – /Q19.

11

OE1

Input

LVTTL/

11k

Enable input synchronized internally to prevent glitching of the

CMOS

Pull-up

Q0 – Q9 and /Q0 – /Q9 outputs.

15

OE2

Input

LVTTL/

11k

Enable input synchronized internally to prevent glitching of the

CMOS

Pull-up

Q10 – Q19 and /Q10 – /Q19 outputs.

4

VCCI

Power

Core VCC connected to 3.3V supply. Bypass with 0.1F in

parallel with 0.01F low ESR capacitors as close to VCC pins as

possible.

17, 32, 33,

VCCO

Power

Output buffer VCC connected to 1.8V nominal supply. All VCCO

40, 41, 48, 49, 64

pins should be connected together on the PCB. Bypass with

0.1F in parallel with 0.01F low ESR capacitors as close to

VCCO pins as possible.

10

GND

Power

Ground.

63, 61, 59, 57, 55

Q0 – Q9

Output

HSTL

Differential clock outputs from CLKA when SEL1 = LOW and

53, 51, 47, 45, 43

from CLKB when SEL1 = HIGH. HSTL outputs (Q and /Q) must

be terminated with 50-to-GND. Q outputs are static when

OE1 = LOW. Unused output pairs may be left floating.

62, 60, 58, 56, 54

/Q0 – /Q9

Output

HSTL

Differential clock outputs (complement) from CLKA when SEL1 =

52, 50, 46, 44, 42

LOW and from CLKB when SEL1 = HIGH. HSTL outputs (Q and

/Q) must be terminated with 50-to-GND. /Q outputs are static

HIGH when OE1 = LOW. Unused output pairs may be left

floating.

39, 37, 35, 31, 29

Q10 – Q19

Output

HSTL

Differential outputs from CLKA when SEL2 = LOW and from

27, 25, 23, 21, 19

CLKB when SEL2 = HIGH. HSTL outputs (Q and /Q) must be

terminated with 50-to-GND. Q outputs are static LOW when

OE2 = LOW. Unused output pairs may be left floating.

38, 36, 34, 30, 28

/Q10 – /Q19

Output

HSTL

Differential outputs (complement) from CLKA when SEL2 = LOW

26, 24, 22, 20, 18

and from CLKB when SEL2 = HIGH. HSTL outputs (Q and /Q)

must be terminated with 50-to-GND. /Q outputs are static HIGH

when OE2 = LOW. Unused output pairs may be left floating.

相关PDF资料 |

PDF描述 |

|---|---|

| SY89827LHGTR | 89827 SERIES, LOW SKEW CLOCK DRIVER, 20 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP64 |

| SY89833ALMGTR | 89833 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC16 |

| SY89833ALMI | 89833 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC16 |

| SY89833ALMITR | 89833 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC16 |

| SY89837UMTR | 89837 SERIES, LOW SKEW CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY89827LHI | 功能描述:IC CLK FANT BUF MUX TRNSL 64TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:Precision Edge® 标准包装:1 系列:HiPerClockS™ 类型:扇出缓冲器(分配),多路复用器 电路数:1 比率 - 输入:输出:2:18 差分 - 输入:输出:是/无 输入:CML,LVCMOS,LVPECL,LVTTL,SSTL 输出:LVCMOS,LVTTL 频率 - 最大:250MHz 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:- 其它名称:800-1923-6 |

| SY89827LHITR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V 500MHz DUAL 1:10 HSTL FANOUT BUFFER/TRANSLATOR WITH 2:1 MUX INPUT |

| SY89827LHY | 功能描述:时钟缓冲器 3.3V Dual 1:20 Diff HSTL Fanout Buffer (I Temp, Lead Free) RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| SY89827LHY TR | 功能描述:时钟缓冲器 3.3V Dual 1:20 Diff HSTL Fanout Buffer (I Temp, Lead Free) RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| SY89827LHYTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V 500MHz DUAL 1:10 HSTL FANOUT BUFFER/TRANSLATOR WITH 2:1 MUX INPUT |

发布紧急采购,3分钟左右您将得到回复。