- 您现在的位置:买卖IC网 > PDF目录98152 > TA1360AFG SPECIALTY CONSUMER CIRCUIT, PQFP80 PDF资料下载

参数资料

| 型号: | TA1360AFG |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封装: | 14 X 20 MM, 0.80 MM HEIGHT, PLASTIC, QFP-80 |

| 文件页数: | 17/110页 |

| 文件大小: | 1614K |

| 代理商: | TA1360AFG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

TA1360AFG

2005-08-18

14

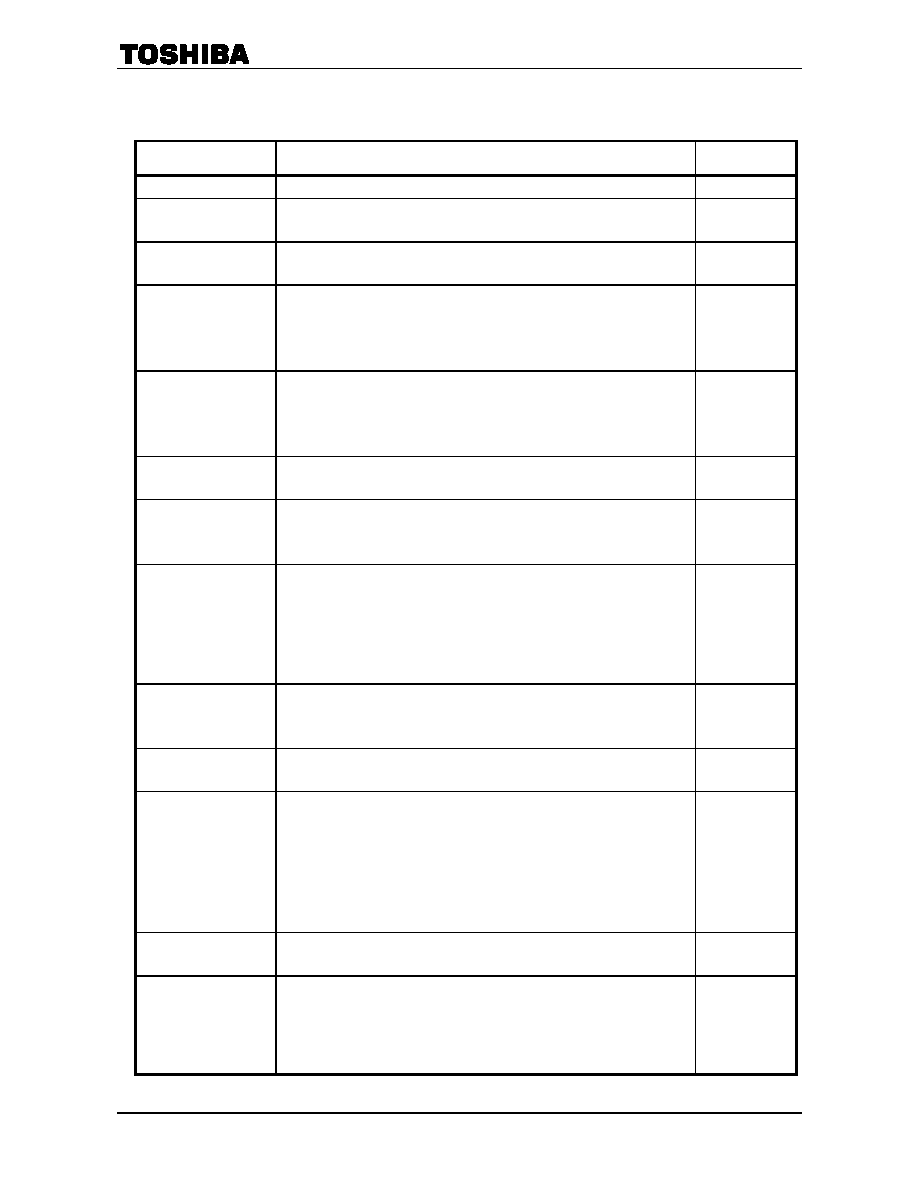

Bus Control Features

Write Mode

Resister Name

Description

Preset Value

H-FREQ1/2

Switches horizontal oscillation frequency. (See the appendix 1)

33.75 kHz

H-DUTY

Switches horizontal output duty.

0: 41% 1: 47%

41%

YUV-SW

Switches YUV input.

0: INPUT-1 (Y1/Cb1/Cr1) 1: INPUT-2 (Y2/Cb2/Cr2)

INPUT-1

DAC 1

Switches DAC controlling output.

0: OPEN (high) 1: ON (low)

Controls 1-bit DAC of open-collector when TEST is 00.

Outputs H/C-SYNC from pin 34 when TEST is 01.

OPEN

DAC 2

Switches DAC controlling output.

0: ON (low), 1: OPEN (high)

Controls 1-bit DAC of open-collector when TEST is 00.

Outputs ACB reference pulse from pin 23 when TEST is 01.

ON

SYNC-SW

Switches sync input.

0: Selects HD/VD input. 1: Selects SYNC input.

HD/VD

HORIZONTAL POSITION

Adjusts horizontal picture position (phase).

0000000:

12.5% 1111111: +12.5%

Note: VP output width (pin 35) varies with a change of horizontal position.

CENTER

CLP-PHS

Switches clamp pulse phase.

0: 0.7-

s (2.5%) width, 1.1-s (3.8%) delay from HD stop phase.

1: 0.7-

s (2.4%) width, 0.2-s (0.7%) delay from HD stop phase

when no signal, 0.8-

s (2.7%) width that is 1.2-s (4.2%) delay from FBP start

phase.

Also switches CP phase of CP-OUT (pin 47).

1.1-

s delay

ACB MODE

Sets ACB mode; Sets converged reference level.

00: ACB OFF (cutoff BUS control), 01: ACB ON (5 IRE),

10: ACB ON (10 IRE) 11: ACB ON (20 IRE)

ACB ON

(10 IRE)

SCP-SW

SCP (sand castle pulse) Switches modes.

0: Internal Mode 1: External input Mode

Internal Mode

HBP-PHS1/2

Switches phase of black-stretch-detection stop pulse.

HBP-PHS1

= 0 and HBP-PHS2 = 0: FBP ± 3%

HBP-PHS1

= 0 and HBP-PHS2 = 1: FBP ± 8%

HBP-PHS1

= 1 and HBP-PHS2 = 0: FBP ± 13%

HBP-PHS1

= 1 and HBP-PHS2 = 1: FBP ± 18%

Leaving Y open and setting the test circuit SW70 to C enable to monitor H/V-BPP

(black-stretch-detection stop pulse) width through pin 70.

±3%

SYNC SEP-LEVEL

Switches Sync SEP-level.

00: 16% 01: 24% 10: 32% 11: 40% (At 1125I/60)

16%

TEST

Test Mode:

Controls 1-bit DAC of open-collector when TEST is 00.

Outputs H/C-SYNC from pin 34, and ACB reference pulse from pin 23 when TEST

is 01.

Do not set TEST to 10/11 for that is shipment TEST Mode.

00

相关PDF资料 |

PDF描述 |

|---|---|

| TA1360ANG | SPECIALTY CONSUMER CIRCUIT, PDIP56 |

| TA1370FG | SYNC SEPARATOR IC, PDSO30 |

| TA1383AFG | SPECIALTY CONSUMER CIRCUIT, PDSO30 |

| TA1384FNG | 2-BAND, VIDEO TUNER, PDSO24 |

| TA1395FNG | 2-BAND, VIDEO TUNER, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TA1360AFG_05 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:YCbCr/YPbPr Signal and Sync Processor for Digital TV, Progressive Scan TV and Double Scan TV |

| TA1360ANG | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:TOSHIBA Bipolar Linear Integrated Circuit Silicon Monolithic |

| TA1360ANG_05 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:YCbCr/YPbPr Signal and Sync Processor for Digital TV, Progressive Scan TV and Double Scan TV |

| TA1370FG | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:SYNC Processor, Frequency Counter IC for TV Component Signals |

| TA1370FG_05 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:SYNC Processor, Frequency Counter IC for TV Component Signals |

发布紧急采购,3分钟左右您将得到回复。