- 您现在的位置:买卖IC网 > PDF目录98158 > TAS3202PAG (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF资料下载

参数资料

| 型号: | TAS3202PAG |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封装: | GREEN, PLASTIC, TQFP-64 |

| 文件页数: | 7/66页 |

| 文件大小: | 817K |

| 代理商: | TAS3202PAG |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

23

22

SCLK

32Clks

LRCLK

LeftChannel

24-BitMode

1

20-BitMode

16-BitMode

15

14

MSB

LSB

SCLK

32Clks

RightChannel

2-ChannelRight-Justified(SonyFormat)StereoInput

T0034-03

19

18

1

19

18

1

0

15

14

15

14

23

22

1

15

14

MSB

LSB

19

18

1

19

18

1

0

15

14

15

14

www.ti.com

SLES208B – JUNE 2009 – REVISED MARCH 2011

3.9.3

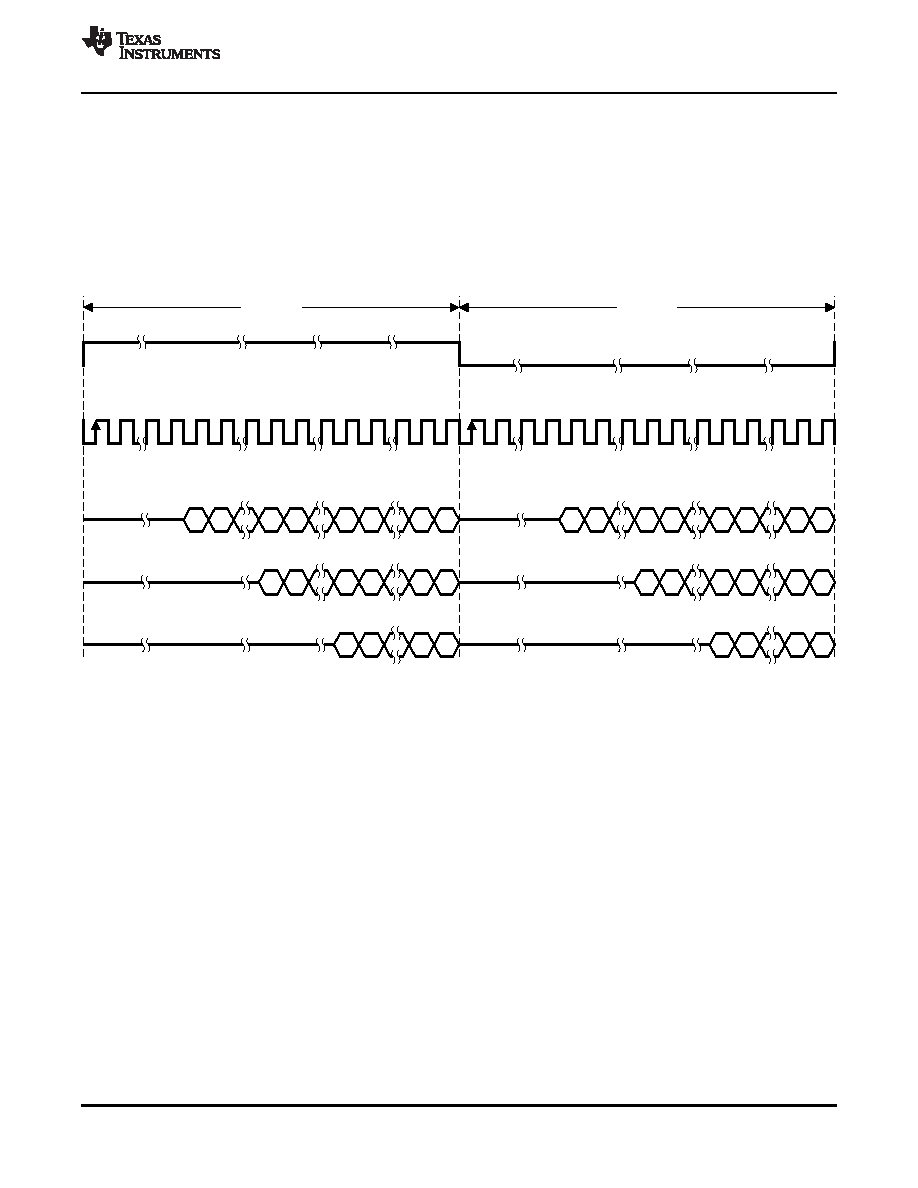

2-Channel Right-Justified Timing

In 2-channel right-justified (RJ) timing, LRCLK is HIGH when left-channel data is transmitted and LOW

when right-channel data is transmitted. SCLK is a bit clock running at 64 × fS which clocks in each bit of

the data. The first bit of data appears on the data lines eight bit-clock periods (for 24-bit data) after LRCLK

toggles. In the RJ mode, the last bit clock before LRCLK transitions always clocks the least-significant bit

(LSB) of data. The data is written MSB first and is valid on the rising edge of the bit clock. The TAS3202

masks unused leading data-bit positions.

Figure 3-4. Right-Justified 64fS Format

3.9.4

SAP Input to SAP Output—Processing Flow

All SAP data format options other than I2S result in a two-sample delay from input to output. If I2S

formatting is used for both the input SAP and the output SAP, the polarity of RCLK must be inverted.

However, if I2S format conversions are performed between input and output, the delay becomes either 1.5

samples or 2.5 samples, depending on the processing clock frequency selected for the audio DSP core

relative to the sample rate of the incoming data.

The I2S format uses the falling edge of LRCLK to begin a sample period, whereas all other formats use

the rising edge of LRCLK to begin a sample period. This means that the input SAP and audio DSP core

operate on sample windows that are 180° out of phase with respect to the sample window used by the

output SAP. This phase difference results in the output SAP outputting a new data sample at the midpoint

of the sample period used by the audio DSP core to process the data. If the processing cycle completes

all processing tasks before the midpoint of the processing sample period, the output SAP outputs this

processed data. However, if the processing time extends past the midpoint of the processing sample

period, the output SAP outputs the data processed during the previous processing sample period. In the

former case, the delay from input to output is 1.5 samples. In the latter case, the delay from input to output

is 2.5 samples.

Copyright 2009–2011, Texas Instruments Incorporated

Physical Characteristics

15

Product Folder Link(s): TAS3202

相关PDF资料 |

PDF描述 |

|---|---|

| TAS3204PAGR | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TAS3204PAG | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TAS3218IPZPR | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS3218IPZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS3218PZPR | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TAS3202PAGR | 功能描述:音频 DSP Hi Perf Dig Aud SOC RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS3204 | 制造商:TI 制造商全称:Texas Instruments 功能描述:AUDIO DSP WITH ANALOG INTERFACE |

| TAS3204EVM | 功能描述:音频 IC 开发工具 TAS3204EVM Eval Mod RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| TAS3204EVM-LC | 制造商:Texas Instruments 功能描述:TAS3204EVM EVALUATION MODULE - Boxed Product (Development Kits) |

| TAS3204PAG | 功能描述:音频 DSP Hi Perf Dual Core DSP/MCU Aud Proc RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。