- 您现在的位置:买卖IC网 > PDF目录98159 > TAS5026IPAGR (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF资料下载

参数资料

| 型号: | TAS5026IPAGR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封装: | GREEN, PLASTIC, TQFP-64 |

| 文件页数: | 13/50页 |

| 文件大小: | 717K |

| 代理商: | TAS5026IPAGR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页

Architecture Overview

15

SLES041B—November 2002

TAS5026

2.2

Reset, Power Down, and Status

The reset, power down, and status circuitry provides the necessary controls to bring the TAS5026 to the initial

inactive condition, achieve low power standby, and report system status.

2.2.1 Reset—RESET

The TAS5026 is placed in the reset mode by setting the RESET terminal low.

RESET is an asynchronous control signal that restores the TAS5026 to its default conditions, sets the valid

1–6 outputs low, and places the PWM in the hard mute state. Volume is immediately set to full attenuation

(there is no ramp down).

As long as the RESET terminal is held low, the device is in the reset state. During reset, all I2C and serial data

bus operations are ignored. Table 2–6 shows the device output signals while RESET is active.

Upon the release of RESET, if POWER_DWN is high, the system performs a 4-ms to 5-ms device initialization

and then ramps the volume up to 0 db using a soft volume update sequence. If MCLK_IN is not active when

RESET is released high, then a 4-ms to 5-ms initialization sequence is produced once MCLK_IN becomes

active.

During device initialization all controls are reset to their initial states. Table 2–7 shows the control settings that

are changed during initialization.

RESET should be applied during power-up initialization or while changing the master slave clock states.

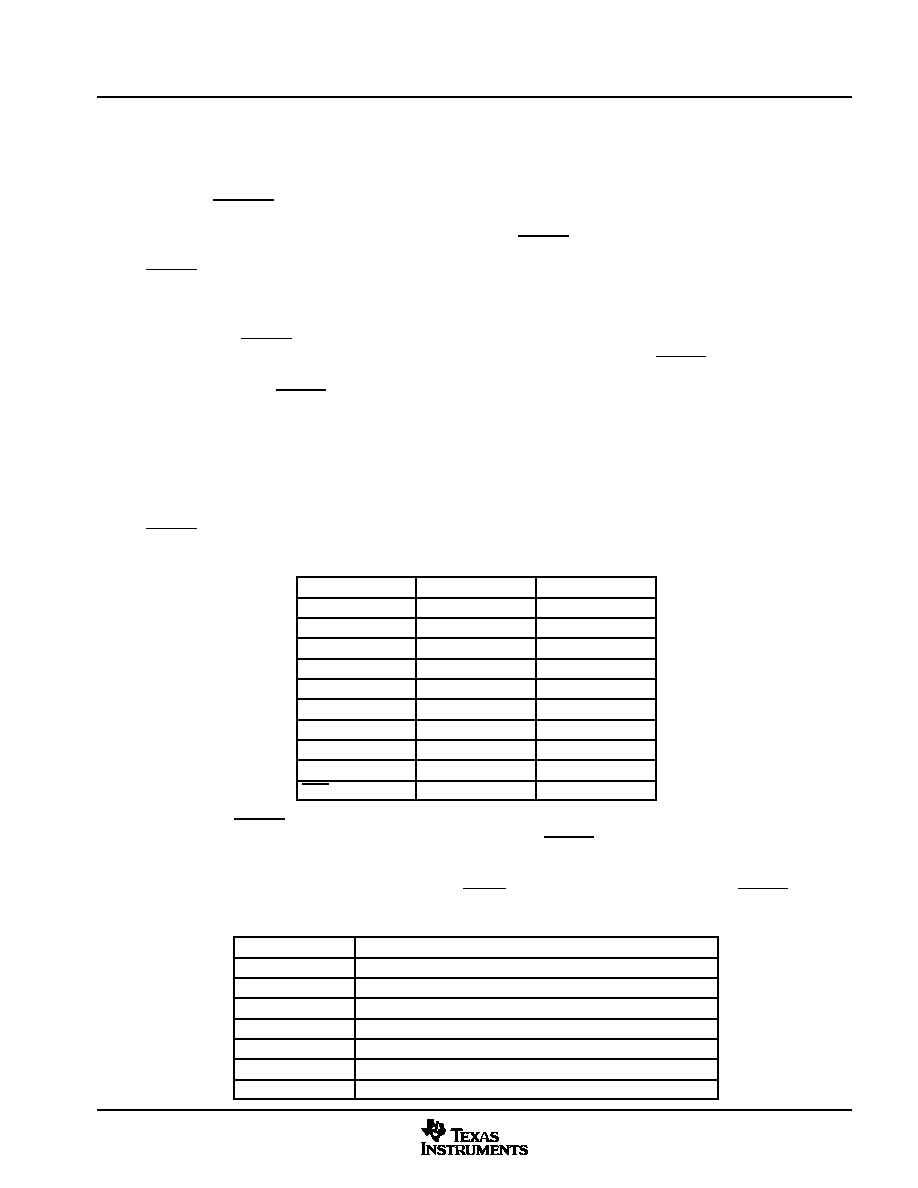

Table 2–6. Device Outputs During Reset

SIGNAL

MODE

SIGNAL STATE

Valid 1–Valid 6

All

Low

PWM P-outputs

All

Low

PWM M-outputs

All

Low

MCLKOUT

All

Low

SCLK

Master

Low

SCLK

Slave

Signal input

LRCLK

Master

Low

LRCLK

Slave

Signal input

SDA

All

Signal input

CLIP

All

High

Because the RESET is an asynchronous control signal, small clicks and pops can be produced during the

application (the leading edge) of this control. However, when RESET is released, the transition from the hard

mute state back to normal operation is performed synchronously using a quiet sequence.

If a completely quiet reset sequence is desired, MUTE should be applied before applying RESET.

Table 2–7. Values Set During Reset

CONTROL

SETTING

Volume

0 dB

MCLK_IN frequency

256

Master/slave mode

M_S terminal state

Auto mute

Enabled

De-emphasis

None

DC offset

0

Interchannel delay

Each channel set at 16 clocks higher then preceding channel

相关PDF资料 |

PDF描述 |

|---|---|

| TAS5026IPAG | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TAS5026IPAGG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TAS5028APAGG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TAS5028APAGRG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TAS5028APAGR | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TAS5026IPAGRG4 | 功能描述:多媒体杂项 Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 类型: 通道数量: 转换速率:540 Mbps 分辨率: 封装 / 箱体:SOIC-16 封装:Tube |

| TAS5026PAG | 功能描述:多媒体杂项 Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 类型: 通道数量: 转换速率:540 Mbps 分辨率: 封装 / 箱体:SOIC-16 封装:Tube |

| TAS5026PAGG4 | 功能描述:多媒体杂项 Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 类型: 通道数量: 转换速率:540 Mbps 分辨率: 封装 / 箱体:SOIC-16 封装:Tube |

| TAS5026PAGR | 功能描述:多媒体杂项 Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 类型: 通道数量: 转换速率:540 Mbps 分辨率: 封装 / 箱体:SOIC-16 封装:Tube |

| TAS5026PAGRG4 | 功能描述:多媒体杂项 Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 类型: 通道数量: 转换速率:540 Mbps 分辨率: 封装 / 箱体:SOIC-16 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。