- 您现在的位置:买卖IC网 > PDF目录98160 > TAS5036BPFCRG4 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP80 PDF资料下载

参数资料

| 型号: | TAS5036BPFCRG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封装: | GREEN, PLASTIC, TQFP-80 |

| 文件页数: | 22/65页 |

| 文件大小: | 950K |

| 代理商: | TAS5036BPFCRG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页

Architecture Overview

23

SLES073—February 2003

TAS5036B

7 Bit Slave Address

R/W

8 Bit Register Address (N)

AA

8 Bit Register Data For

Address (N)

A

8 Bit Register Data For

Address (N)

A

7

6

5

432

1

0

7

6

54

32

1

0

7

6

54

32

1

0

7

6

54

32

1

0

Start

Stop

SDA

SCL

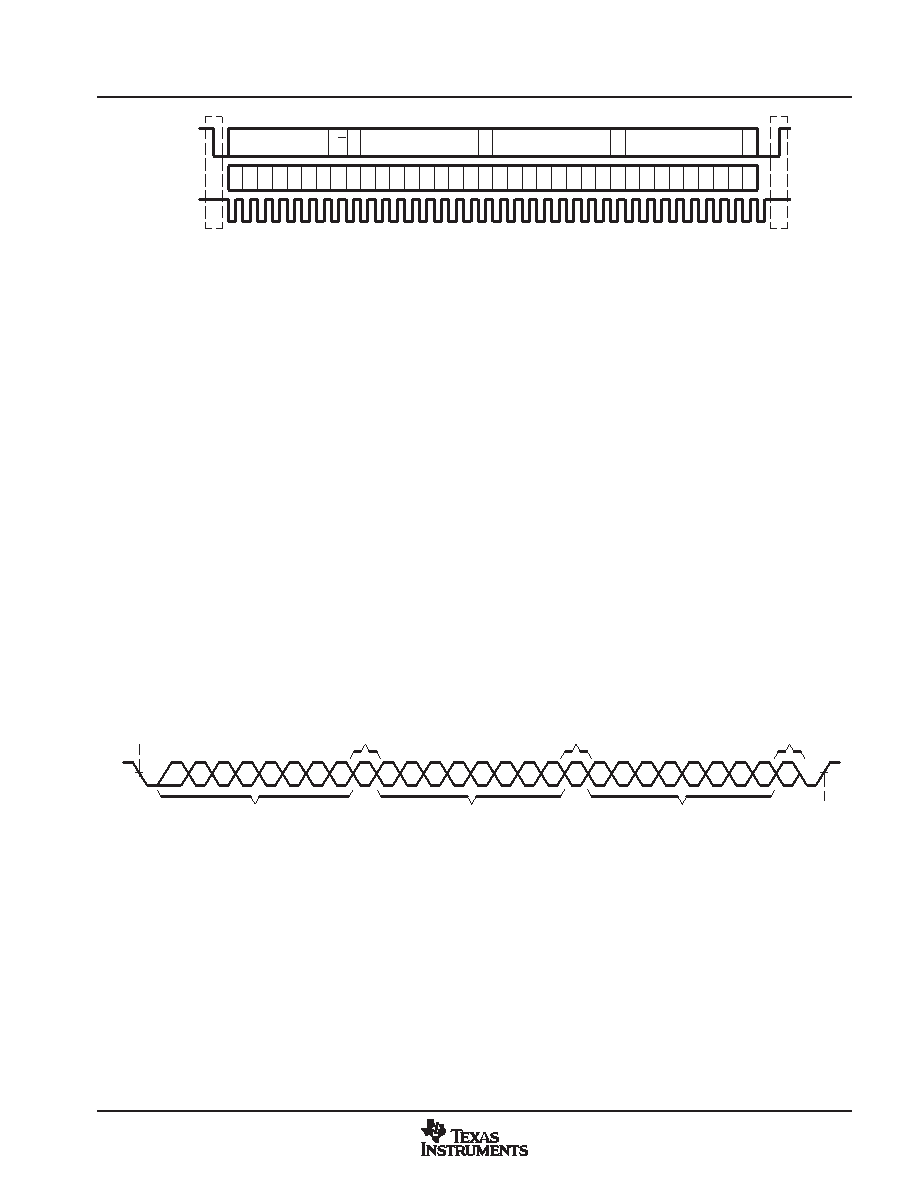

Figure 213. Typical I2C Sequence

There are no limits on the number of bytes that can be transmitted between start and stop conditions. When

the last word transfers, the master generates a stop condition to release the bus. A generic data transfer

sequence is also shown in Figure 213.

The 7-bit address for the TAS5036B is 001101X, where X is a programmable address bit. Using the CS0

terminal on the device, the LSB address bit is programmable to permit two devices to be used in a system.

These two addresses are licensed I2C addresses and do not conflict with other licensed I2C audio devices.

To communicate with the TAS5036B, the I2C master uses 0011010 if CS0=0 and 0011011 if CS0=1. In addition

to the 7-bit device address, an 8-bit register address is used to direct communication to the proper register

location within the device interface.

Read and write operations to the TAS5036B can be done using single byte or multiple byte data transfers.

2.5.1 Single Byte Write

As shown in Figure 214, a single byte data write transfer begins with the master device transmitting a start

condition followed by the I2C device address and the read/write bit. The read/write bit determines the direction

of the data transfer. For a write data transfer, the read/write bit is 0. After receiving the correct I2C device

address and the read/write bit, the TAS5036B device responds with an acknowledge bit. Next, the master

transmits the address byte or bytes corresponding to the TAS5036B internal memory address being

accessed. After receiving the address byte, the TAS5036B again responds with an acknowledge bit. Next, the

master device transmits the data byte to be written to the memory address being accessed. After receiving

the data byte, the TAS5036B again responds with an acknowledge bit. Finally, the master device transmits

a stop condition to complete the single byte data write transfer.

A6

A5

A4

A3

A2

A1

A0

R/W ACK A7

A6

A5

A4

A3

A2

A1

A0

ACK

D7

D6

D5

D4

D3

D2

D1

D0

ACK

Start Condition

Stop

Condition

Acknowledge

I2C Device Address and

Read/Write Bit

Register Address

Data Byte

Figure 214. Single Byte Write Transfer

2.5.2 Multiple Byte Write

A multiple byte data write transfer is identical to a single byte data write transfer except that multiple data bytes

are transmitted by the master device to TAS5036B as shown in Figure 215. After receiving each data byte,

the TAS5036B responds with an acknowledge bit.

相关PDF资料 |

PDF描述 |

|---|---|

| TAS5036BPFCG4 | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| TAS5036IPFCR | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| TAS5036IPFC | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| TAS5036PFCR | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| TAS5036PFC | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TAS5036CPAG | 制造商:TI 制造商全称:Texas Instruments 功能描述:SIX CHANNEL DIGITAL AUDIO PWM PROCESSOR |

| TAS5036IPFC | 功能描述:音频 DSP Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS5036IPFCG4 | 功能描述:音频 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS5036IPFCR | 功能描述:音频 DSP Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS5036IPFCRG4 | 功能描述:音频 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。