- 您现在的位置:买卖IC网 > PDF目录98170 > TC3405VQRTR 4-CH 16-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO16 PDF资料下载

参数资料

| 型号: | TC3405VQRTR |

| 元件分类: | ADC |

| 英文描述: | 4-CH 16-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO16 |

| 封装: | QSOP-16 |

| 文件页数: | 8/12页 |

| 文件大小: | 68K |

| 代理商: | TC3405VQRTR |

5

TC3405

TC3405-1 12/7/99

16-Bit Low Cost, Low Power

∑ – A/D Converter

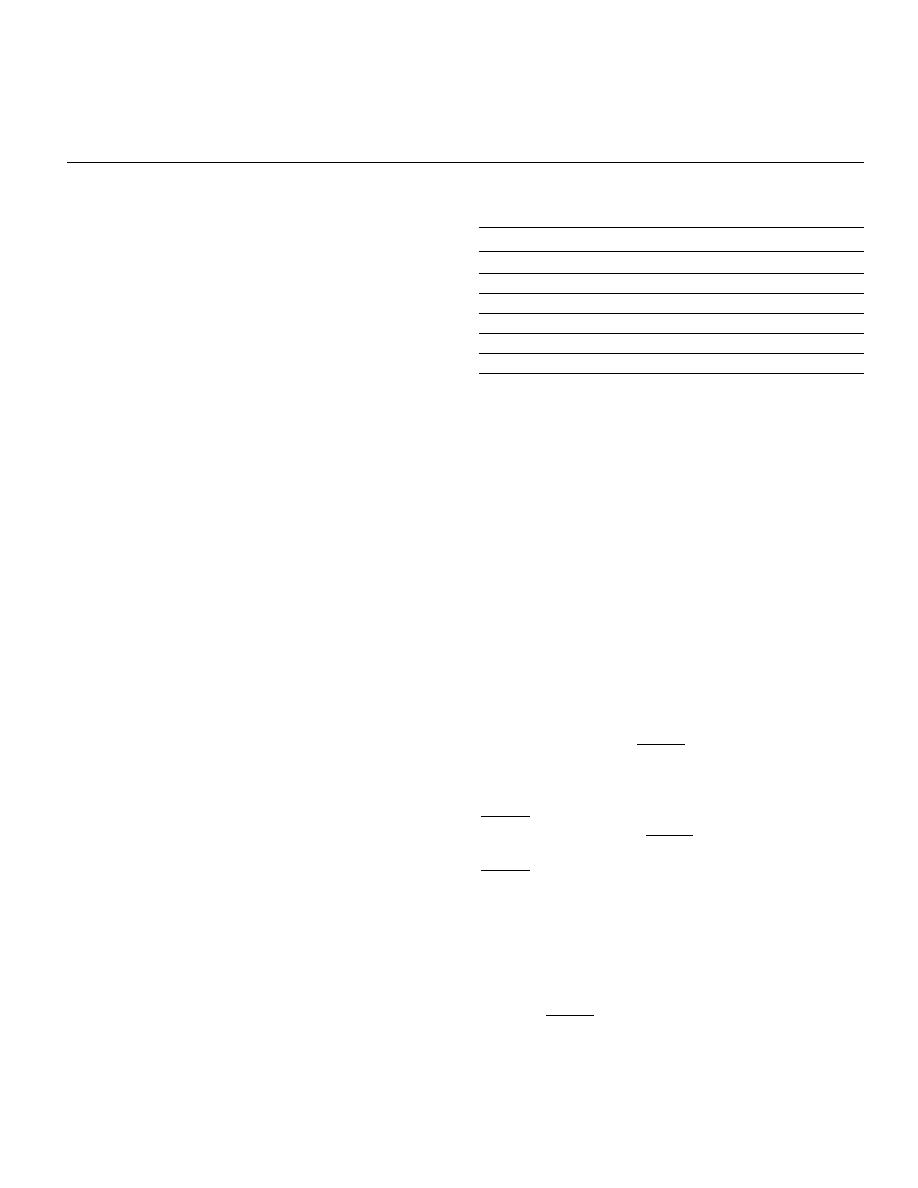

Table 1. Data Conversion Word vs. Voltage Input

(REFIN = 1.205V)

Data Word

INn+ – INn– (Volts)

0111 1111 1111 1111

2.38596 (Positive Full Scale)

0000 0000 0000 0001

72.8 E – 6

0000 0000 0000 0000

0

1111 1111 1111 1111

–72.8 E – 6

1000 0000 0000 0001

–2.38596 (Negative Full Scale)

1000 0000 0000 0000

Reserved Code

The SCLK input has a filter which rejects any positive or

negative pulse width less than 50ns to reduce noise. The

rejection width of this pulse can vary between 50ns and

750ns depending on processing parameters and supply

voltage.

Figure 3 shows a truth table for determining the mode of

operation for the TC3405 part by recording the value of

SDAT for SCLK in a high, then low, then high state. For

example, if SCLK goes through a 1-0-1 transition and the

corresponding values of SDAT are 1-1-0, then the SCLK

falling edge started a new data conversion. A 0-1-0 for SDAT

would have indicated a resolution reduction had occurred.

This is useful if the microcontroller has a watchdog reset or

otherwise loses track of where the TC3405 part is in the

conversion and data readout sequence. The microcontroller

can simply transition SCLK until it “finds” a Start Conversion

condition.

VDD Monitor

On the TC3405 the RESET output is high provided the

voltage at VTH is greater than the internal voltage refererence.

This reference is the same value as the voltage appearing

at REFOUT. When VTH is less than the internal reference,

RESET is pulled low. When VTH rises above the internal

reference voltage again RESET is held low for the reset

active timeout period, t9, before being released high. The

RESET output is guaranteed to be valid for VDD = 1.3V to

5.5V.

When used to generate a power-on or brown-out reset

an external resistor network is required to divide the appro-

priate VDD threshold down to 1.23V at the VTH input (see

Figure 1). For example, to generate a POR for a VDD at 3V-

10%, then the values of R1 and R2 should be 137k

and

115k

respectively.

Since RESET is an open drain it can be wire-OR’ed with

another open drain or external switch if desired.

GENERAL THEORY OF OPERATION

The TC3405 is a 16-bit sigma-delta A/D converter. It

has one differential input, three single ended inputs, an

analog multiplexer and a VDD monitor with reset generator.

The following is a detailed description of the device’s key

components. Refer to the A/D Operational Flowchart and

Figures 2 through 5.

A/D Converter Operation

When the TC3405 is not converting, it is in sleep mode

with both the SCLK and SDAT lines high. An A/D conversion

is initiated by a high to low transition on the SCLK line at

which time the internal clock of the TC3405 is started and

the address value (A0 and A1) is internally latched. The

address value steers the analog multiplexer to select the

input channel to be converted. Each additional high to low

transition of SCLK (following the initial SCLK falling edge)

and during the time interval t4 will decrement the conversion

accuracy by one bit and reduce the conversion time by one

half. The time interval t4 is referred to as the resolution

reduction window. The minimum conversion resolution is 10

bits so any more than 6 SCLK transitions during t4 will be

ignored.

After each high to low transition of SCLK the SDAT

output is driven high by the TC3405 to acknowledge that the

conversion has been decremented. When the SCLK returns

high or the t4 interval ends, the SDAT line returns low (see

Figure 2). When the conversion is complete SDAT is driven

high. The 3405 now enters sleep mode and the conversion

value can be read as a serial data word on the SDAT line.

Reading the Data Word

After the conversion is complete and SDAT goes high,

the conversion value can be clocked serially onto the SDAT

line by high to low transitions of the SCLK. The data word is

in two’s compliment format with the sign bit clocked onto the

SDAT line first followed by the MSB and ending in the LSB.

For a 16 bit conversion the data word would consist of a sign

bit follwed by 15 magnitude bits, Table 1 shows the data

word versus input voltage for a 16 bit conversion. Note that

the full scale input voltage range is

±(2 REFIN– 1LSB). When

REFOUT is fed back directly to REFIN, an LSB is 73V for a

16 bit conversion, as REFOUT is typically 1.193V.

Figure 4 shows typical SCLK and SDAT waveforms for

16, 12 and 10 bit conversions. Note that any complete

convert and read cycle requires 17 clock pulses. Up to six of

these can occur in the resolution reduction window, t4, to

decrement accuracy while the remaining pulses clock out

the conversion data word.

相关PDF资料 |

PDF描述 |

|---|---|

| TC3405VQRRT | 4-CH 16-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO16 |

| TC35273 | SPECIALTY CONSUMER CIRCUIT, PBGA201 |

| TC4066BFN | QUAD 1-CHANNEL, SGL POLE SGL THROW SWITCH, PDSO14 |

| TC4066BP | QUAD 1-CHANNEL, SGL POLE SGL THROW SWITCH, PDIP14 |

| TC4066BFT | QUAD 1-CHANNEL, SGL POLE SGL THROW SWITCH, PDSO14 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TC341 | 制造商:TI 制造商全称:Texas Instruments 功能描述:780X488 PIXEL CCD IMAGE SENSOR |

| TC341-20 | 功能描述:视频 IC 780 X 488-Pixel CCD Image Sensor RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| TC341-30 | 功能描述:视频 IC 780 X 488-Pixel CCD Image Sensor RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| TC341-40 | 功能描述:视频 IC 780 X 488-Pixel CCD Image Sensor RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| TC3417D-101M | 制造商:PRODUCTWELL 制造商全称:PRODUCTWELL 功能描述:TOROID INDUCTORS |

发布紧急采购,3分钟左右您将得到回复。