- 您现在的位置:买卖IC网 > PDF目录85414 > TDA4854NB (NXP SEMICONDUCTORS) HORIZ/VERT DEFLECTION IC, PDIP32 PDF资料下载

参数资料

| 型号: | TDA4854NB |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 偏转 |

| 英文描述: | HORIZ/VERT DEFLECTION IC, PDIP32 |

| 封装: | PLASTIC, SDIP-32 |

| 文件页数: | 61/63页 |

| 文件大小: | 318K |

| 代理商: | TDA4854NB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页当前第61页第62页第63页

1999 Jul 13

7

Philips Semiconductors

Product specication

I2C-bus autosync deection controllers for

PC/TV monitors

TDA4853; TDA4854

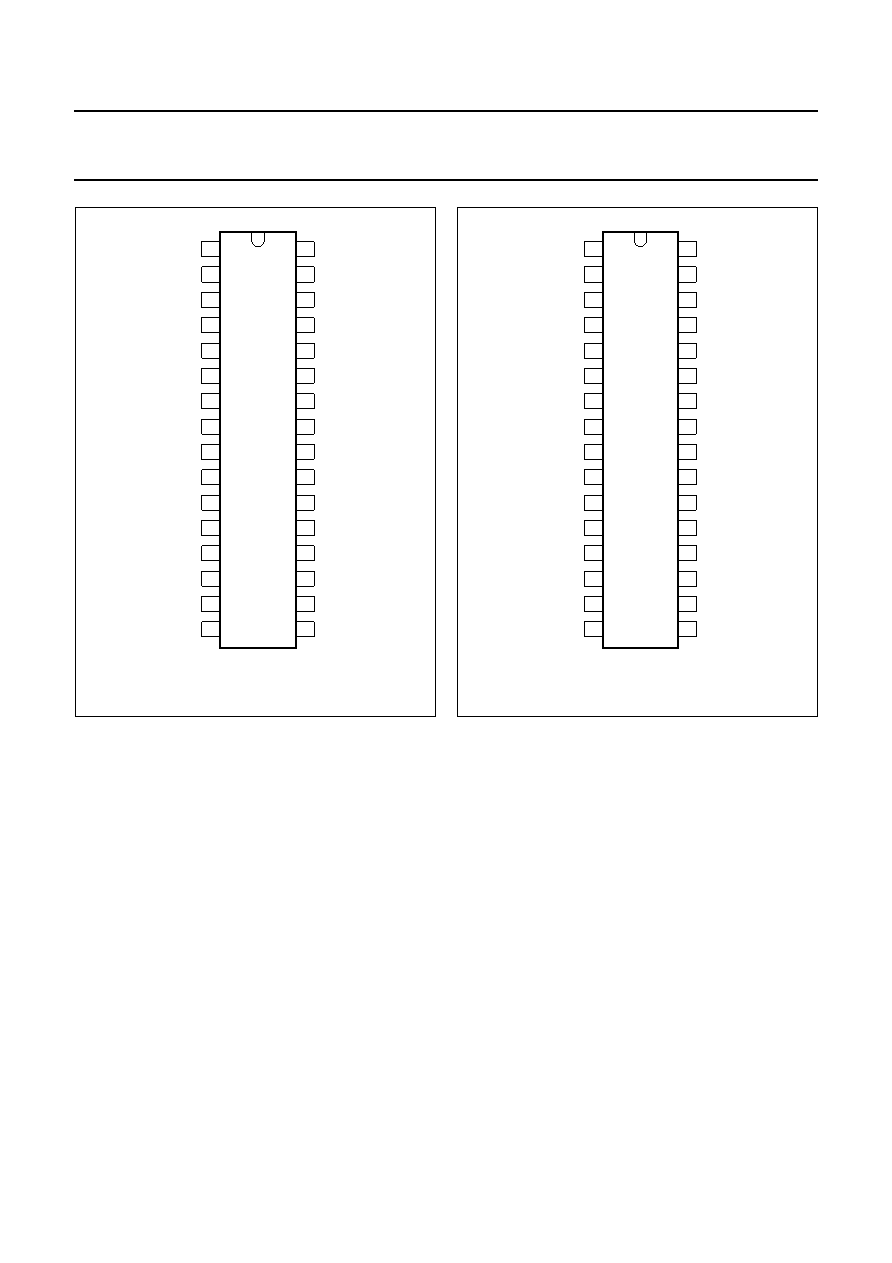

Fig.3 Pin configuration for TDA4853.

handbook, halfpage

TDA4853

MGM066

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

HFLB

XRAY

BOP

BSENS

BIN

BDRV

PGND

HDRV

XSEL

VCC

EWDRV

VOUT2

VOUT1

VSYNC

i.c.

HSMOD

HPLL2

HCAP

HBUF

HPLL1

HREF

SGND

VCAP

VREF

VAGC

VSMOD

ASCOR

SDA

HSYNC

CLBL

SCL

HUNLOCK

Fig.4 Pin configuration for TDA4854.

handbook, halfpage

TDA4854

MGM067

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

HFLB

XRAY

BOP

BSENS

BIN

BDRV

PGND

HDRV

XSEL

VCC

EWDRV

VOUT2

VOUT1

VSYNC

FOCUS

HSMOD

HPLL2

HCAP

HBUF

HPLL1

HREF

SGND

VCAP

VREF

VAGC

VSMOD

ASCOR

SDA

HSYNC

CLBL

SCL

HUNLOCK

FUNCTIONAL DESCRIPTION

Horizontal sync separator and polarity correction

HSYNC (pin 15) is the input for horizontal synchronization

signals, which can be DC-coupled TTL signals (horizontal

or composite sync) and AC-coupled negative-going video

sync signals. Video syncs are clamped to 1.28 V and

sliced at 1.4 V. This results in a fixed absolute slicing level

of 120 mV related to top sync.

For DC-coupled TTL signals the input clamping current is

limited. The slicing level for TTL signals is 1.4 V.

The separated sync signal (either video or TTL) is

integrated on an internal capacitor to detect and normalize

the sync polarity.

Normalized horizontal sync pulses are used as input

signals for the vertical sync integrator, the PLL1 phase

detector and the frequency-locked loop.

The presence of equalization pulses is allowed for correct

function of the PLL1 phase detector only in TV mode.

Vertical sync integrator

Normalized composite sync signals from HSYNC are

integrated on an internal capacitor in order to extract

vertical sync pulses. The integration time is dependent on

the horizontal oscillator reference current at HREF

(pin 28). The integrator output directly triggers the vertical

oscillator.

Vertical sync slicer and polarity correction

Vertical sync signals (TTL) applied to VSYNC (pin 14) are

sliced at 1.4 V. The output signal of the sync slicer is

integrated on an internal capacitor to detect and normalize

the sync polarity. The output signals of vertical sync

integrator and sync normalizer are disjuncted before they

are fed to the vertical oscillator.

相关PDF资料 |

PDF描述 |

|---|---|

| TDA7052A/N2 | 1 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDIP8 |

| TDA7052AT/N2 | 1 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDSO8 |

| TDA9178/N1 | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| TDA9178N | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| TDA9178T/N1 | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TDA4855 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Autosync Deflection Controller ASDC |

| TDA4856 | 制造商:Phil 功能描述:Semiconductor |

| TDA4857 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:I2C-bus autosync deflection controller for PC monitors |

| TDA4857PS | 制造商:NXP Semiconductors 功能描述:HORIZ/VERT DEFLECTION IC, PDIP32 |

| TDA4858 | 制造商:NXP Semiconductors 功能描述:Video/TV Circuit, Video DEFLECTION Circuit, 32 Pin, Plastic, SDIP |

发布紧急采购,3分钟左右您将得到回复。