- 您现在的位置:买卖IC网 > PDF目录85416 > TDA8764AHL/6/C1 (NXP SEMICONDUCTORS) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP32 PDF资料下载

参数资料

| 型号: | TDA8764AHL/6/C1 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP32 |

| 封装: | PLASTIC, SOT-401-1, LQFP-32 |

| 文件页数: | 2/29页 |

| 文件大小: | 186K |

| 代理商: | TDA8764AHL/6/C1 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

2000 Jul 03

10

Philips Semiconductors

Product specication

10-bit high-speed low-power ADC

TDA8764A

Notes

1.

The rise and fall times of the clock signal must not be less than 0.5 ns.

2. The input admittance is

3. Analog input voltages producing code 0 up to and including code 1023:

a) Voffset(B) (offset voltage BOTTOM) is the difference between the analog input which produces data equal to 00

and the reference voltage BOTTOM (VRB) at Tamb =25 °C.

b) Voffset(T) (offset voltage TOP) is the difference between VRT (reference voltage TOP) and the analog input which

produces data outputs equal to code 1023 at Tamb =25 °C.

4. In order to ensure the optimum linearity performance of such converter architecture the lower and upper extremities

of the converter reference resistor ladder (corresponding to output codes 0 and 1023 respectively) are connected to

pins VRB and VRT via offset resistors ROB and ROT as shown in Fig.4.

a) The current flowing into the resistor ladder is

and the full-scale input range at the converter,

to cover code 0 to 1023, is

b) Since RL, ROB and ROT have similar behaviour with respect to process and temperature variation, the ratio

will be kept reasonably constant from device to device. Consequently variation of the output

codes at a given input voltage depends mainly on the difference VRT VRB and its variation with temperature and

supply voltage. When several ADCs are connected in parallel and fed with the same reference source, the

matching between each of them is then optimized.

5.

6. The analog bandwidth is defined as the maximum input sine wave frequency which can be applied to the device.

No glitches greater than 2 LSBs, nor any significant attenuation are observed in the reconstructed signal.

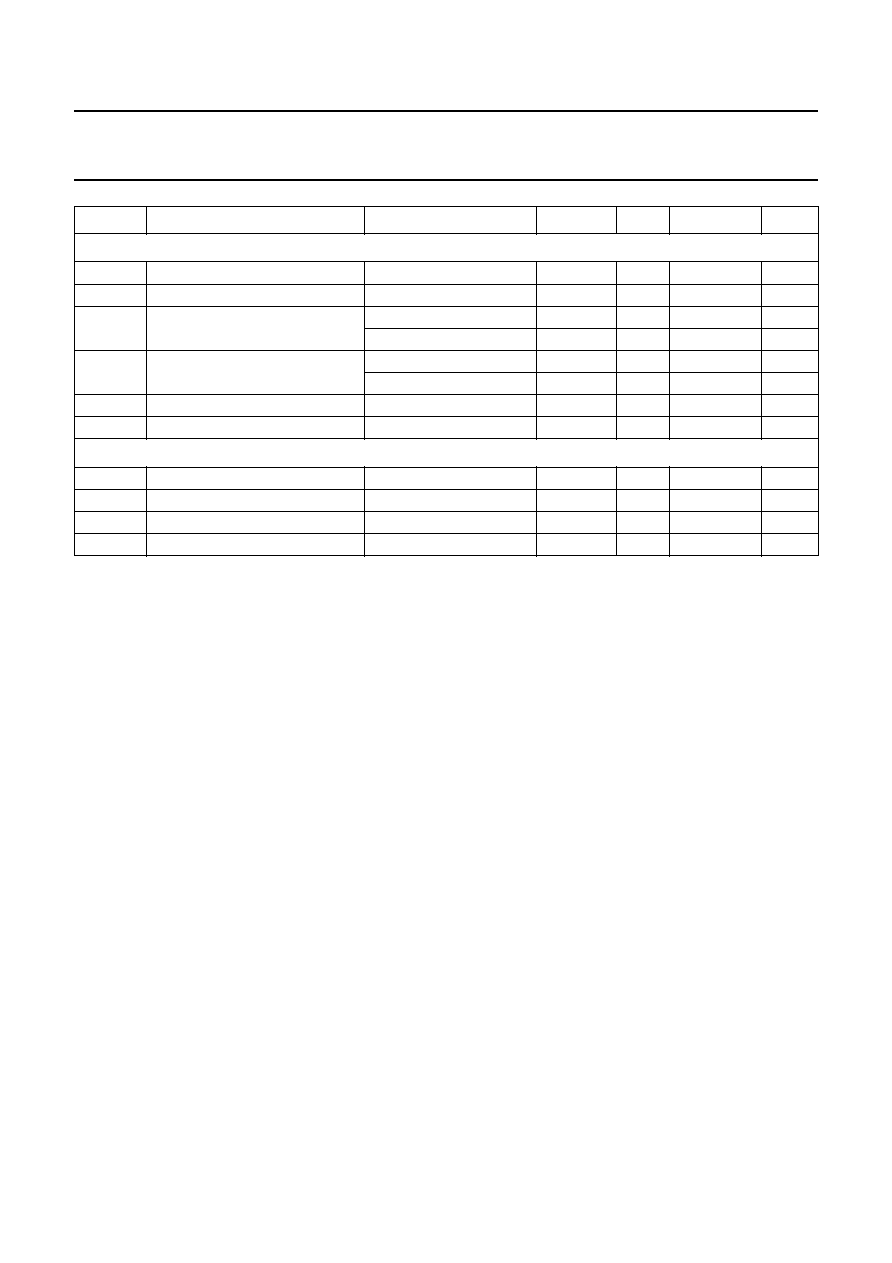

Timing (fclk = 60 MHz; CL = 10 pF); see Fig.5 and note 10

tds

sampling delay time

0.7

2

ns

th

output hold time

4

ns

td

output delay time TDA8764ATS

VCCO = 2.7 V

10

14

ns

VCCO = 3.3 V

913

ns

td

output delay time TDA8764AHL

VCCO = 2.7 V

13

17

ns

VCCO = 3.3 V

12

16

ns

CL

digital output load capacitance

10

pF

SR

slew rate

VCCO = 2.7 V

0.2

0.3

V/ns

3-state output delay times (fclk = 60 MHz); see Fig.6

tdZH

enable HIGH

VCCO = 3.3 V

16

20

ns

tdZL

enable LOW

VCCO = 3.3 V

30

34

ns

tdHZ

disable HIGH

VCCO = 3.3 V

25

30

ns

tdLZ

disable LOW

VCCO = 3.3 V

23

27

ns

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

Y

i

1

R

i

-----

j

ωCi

+

=

I

L

V

RT

V

RB

–

R

OB

R

L

R

OT

++

------------------------------------------

=

V

I

R

L

I

L

×

R

L

R

OB

R

L

R

OT

++

------------------------------------------

==

V

(

RT

×

V

RB )

–

0.

˙ 8375

V

(

RT

V

RB )

–

×

=

R

L

R

OB

R

L

R

OT

++

------------------------------------------

E

G

V

1023

V

0

–

() V

i(p-p)

–

V

i(p-p)

----------------------------------------------------

100

×

=

相关PDF资料 |

PDF描述 |

|---|---|

| TDA8764ATS/6/C1 | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TDA8775GB-S | TRIPLE, PARALLEL, WORD INPUT LOADING, 0.01 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| TDA8775G/C1,151 | TRIPLE, PARALLEL, WORD INPUT LOADING, 0.01 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| TDF8704T/4D-T | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO24 |

| TDF8704T/4D | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TDA8764ATS | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:10-bit high-speed low-power ADC |

| TDA8764ATS/6 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:10-bit high-speed low-power ADC |

| TDA8764HL/4 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:10-bit high-speed low-power ADC with internal reference regulator |

| TDA8764HL/8 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:10-bit high-speed low-power ADC with internal reference regulator |

| TDA8764TS | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:10-bit high-speed low-power ADC with internal reference regulator |

发布紧急采购,3分钟左右您将得到回复。