- 您现在的位置:买卖IC网 > PDF目录98235 > TLC1549IDRG4 (TEXAS INSTRUMENTS INC) 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 PDF资料下载

参数资料

| 型号: | TLC1549IDRG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| 封装: | GREEN, SOIC-8 |

| 文件页数: | 14/19页 |

| 文件大小: | 407K |

| 代理商: | TLC1549IDRG4 |

TLC1549C, TLC1549I, TLC1549M

10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL

SLAS059C – DECEMBER 1992 – REVISED MARCH 1995

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

detailed description

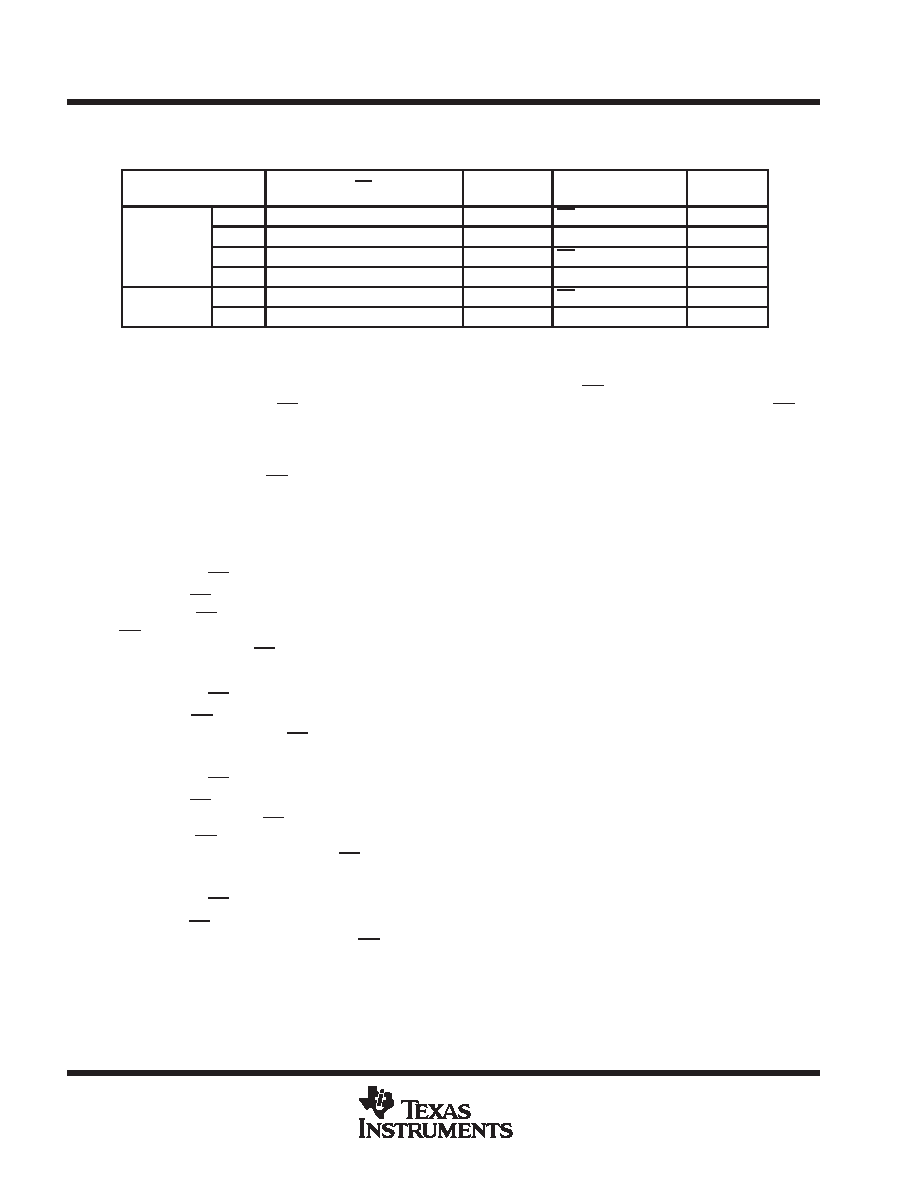

Table 1. Mode Operation

MODES

CS

NO. OF

I/O CLOCKS

MSB AT Terminal 6

TIMING

DIAGRAM

Mode 1

High between conversion cycles

10

CS falling edge

Figure 6

Fast Modes

Mode 2

Low continuously

10

Within 21

s

Figure 7

Fast Modes

Mode 3

High between conversion cycles

11 to 16

CS falling edge

Figure 8

Mode 4

Low continuously

16

Within 21

s

Figure 9

Slow Modes

Mode 5

High between conversion cycles

11 to 16

CS falling edge

Figure 10

Slow Modes

Mode 6

Low continuously

16

16th clock falling edge

Figure 11

This timing also initiates serial interface communication.

No more than 16 clocks should be used.

All the modes require a minimum period of 21

s after the falling edge of the tenth I/O CLOCK before a new

transfer sequence can begin. During a serial I/O CLOCK data transfer, CS must be active (low) so that I/O

CLOCK is enabled. When CS is toggled between data transfers (modes 1, 3, and 5), the transitions at CS are

recognized as valid only if the level is maintained for a minimum period of 1.425

s after the transition. If the

transfer is more than ten I/O clocks (modes 3, 4, 5, and 6), the rising edge of the eleventh clock must occur within

9.5

s after the falling edge of the tenth I/O CLOCK; otherwise, the device could lose synchronization with the

host serial interface and CS has to be toggled to restore proper operation.

fast modes

The TLC1549 is in a fast mode when the serial I/O CLOCK data transfer is completed within 21

s from the falling

edge of the tenth I/O CLOCK. With a ten-clock serial transfer, the device can only run in a fast mode.

mode 1: fast mode, CS inactive (high) between transfers, 10-clock transfer

In this mode, CS is inactive (high) between serial I/O CLOCK transfers and each transfer is ten clocks long. The

falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state. The rising edge

of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified delay time.

Also, the rising edge of CS disables I/O CLOCK within a setup time plus two falling edges of the internal system

clock.

mode 2: fast mode, CS active (low) continuously, 10-clock transfer

In this mode, CS is active (low) between serial I/O CLOCK transfers and each transfer is ten clocks long. After

the initial conversion cycle, CS is held active (low) for subsequent conversions. Within 21

s after the falling

edge of the tenth I/O CLOCK, the MSB of the previous conversion appears at DATA OUT.

mode 3: fast mode, CS inactive (high) between transfers, 11- to 16-clock transfer

In this mode, CS is inactive (high) between serial I/O CLOCK transfers and each transfer can be 11 to 16 clocks

long. The falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state. The

rising edge of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified

delay time. Also, the rising edge of CS disables I/O CLOCK within a setup time plus two falling edges of the

internal system clock.

mode 4: fast mode, CS active (low) continuously, 16-clock transfer

In this mode, CS is active (low) between serial I/O CLOCK transfers and each transfer must be exactly 16 clocks

long. After the initial conversion cycle, CS is held active (low) for subsequent conversions. Within 21

s after

the falling edge of the tenth I/O CLOCK, the MSB of the previous conversion appears at DATA OUT.

slow modes

In a slow mode, the serial I/O CLOCK data transfer is completed after 21

s from the falling edge of the tenth

I/O CLOCK.

相关PDF资料 |

PDF描述 |

|---|---|

| TLC1549CDG4 | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLC1549CD | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLC1549MFKR | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC20 |

| TLC1549MFK | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC20 |

| TLC1549IPE4 | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDIP8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLC1549IP | 功能描述:模数转换器 - ADC Single Input Ser RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLC1549IPE4 | 功能描述:模数转换器 - ADC 10-Bit 38 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLC1549M | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL |

| TLC1549MFK | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL |

| TLC1549MJG | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL |

发布紧急采购,3分钟左右您将得到回复。