- 您现在的位置:买卖IC网 > PDF目录98249 > TLV1570IDW (TEXAS INSTRUMENTS INC) 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF资料下载

参数资料

| 型号: | TLV1570IDW |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封装: | GREEN, SOIC-20 |

| 文件页数: | 27/32页 |

| 文件大小: | 634K |

| 代理商: | TLV1570IDW |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页

TLV1570

2.7 V TO 5.5 V 8-CHANNEL 10-BIT 1.25-MSPS

SERIAL ANALOG-TO-DIGITAL CONVERTER

SLAS169B – DECEMBER 1997– REVISED OCTOBER 2000

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

sampling frequency, fs

The TLV1570 requires 16 SCLKs for each sampling and conversion, therefore the equivalent maximum

sampling frequency achievable with a given SCLK frequency is:

fs(MAX) = (1/16)fSCLK

power down

The TLV1570 offers two different power-down options. With autopower-down mode enabled, (DI4=0) the ADC

proceeds to power down if FS is not detected on the 17th falling SCLK edge of a cycle (a cycle starts with FS

being detected on a falling edge of SCLK) in DSP mode and after 16 SCLKs in

C mode. The TLV1570 will

recover from auto power down when FS goes high in DSP mode or when the next SCLK comes in

C mode.

In the case of software power down, the ADC goes to the software power-down state one cycle after CR.DI15

is set to 1. Unlike autopower down which recovers in 1 SCLK, software power down takes 16 SCLKs to recover.

DESCRIPTION

AUTOPOWER DOWN

SOFTWARE

POWERDOWN

CS = DVDD

Maximum power down dissipation current

300

A

10

A

Comparator

Power down

Powerdown

Clock buffer

Power down

Powerdown

Reference

Active

Powerdown

Register

Not saved

Minimum power down time

1 SCLK

1

s

Minimum resume time

1 SCLK

800 ns

Power down

DSP mode

No FS present one SCLK after previous conversion completed

CR.DI15 set to 1

Power down

Microprocessor mode (FS = 1)

SCLK stopped after previous conversion completed

CR.DI15 set to 1

Power up

DSP mode

FS present

CR.DI15 set to 1

Power up

Microprocessor mode (FS = 1)

SCLK present

CR.DI15 set to 1

Only in DSP mode is input buffer of clock in power-down mode.

The software power down enable/disable bit is not acted until the start of the next cycle (see section configuring the TLV1570 for more information.

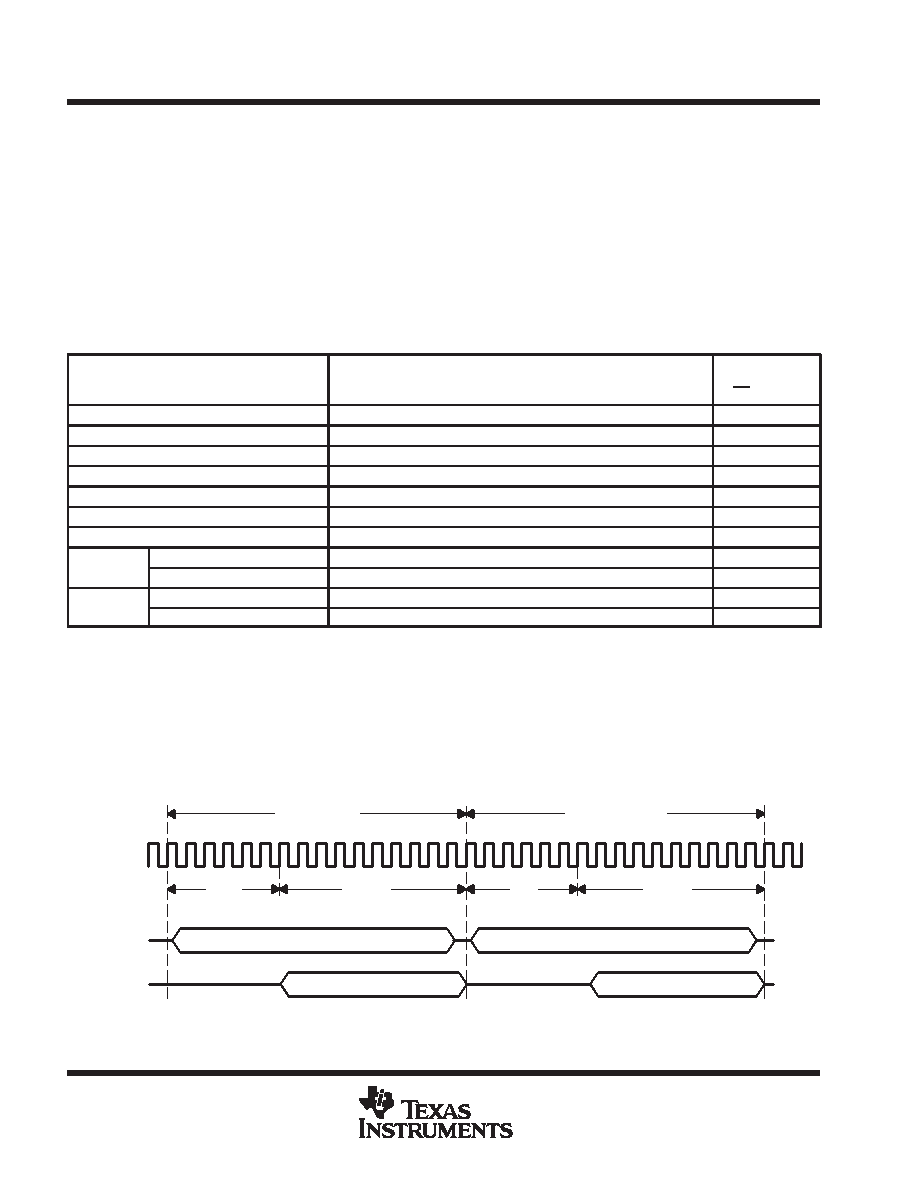

configuring the TLV1570

The TLV1570 is to be configured by writing the control bits to SDIN. The configuration will not take affect until

the next cycle. A new configuration is needed for each conversion. Once the channel input and other options

are selected, the conversion takes place in the next cycle. Conversion results are shifted out as conversion

progresses ( see Figure 2).

17

32

One Cycle

Second Cycle

ts

tconv

ts

tconv

Result 0

Result 1

Configure Data 1

Configure Data 2

SCLK

SDOUT

SDIN

Figure 2. TLV1570 Configuration Cycle Timing

相关PDF资料 |

PDF描述 |

|---|---|

| TLV1570CPW | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV1570IDWR | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV1570IPWRG4 | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV1570CDWR | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV1570IPWG4 | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLV1570IDWG4 | 功能描述:模数转换器 - ADC 10-Bit 1.25 MSPS 8-Ch DSP RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV1570IDWR | 制造商:Texas Instruments 功能描述: |

| TLV1570IPW | 功能描述:模数转换器 - ADC 10bit 1.25MSPS Ser RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV1570IPWG4 | 功能描述:模数转换器 - ADC 10-Bit 1.25 MSPS 8-Ch DSP RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV1570IPWR | 功能描述:模数转换器 - ADC 10-Bit 1.25 MSPS 8-Ch DSP RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。